於本周舉行的2025年IEEE國際電子會議(IEDM)上,比利時微電子研究中心(imec)發表了首篇針對3D 高頻寬記憶體(HBM)與圖形處理器(GPU)堆疊元件(HBM-on-GPU)的系統技術協同優化(STCO)熱學研究,這種元件是下一代人工智慧(AI)應用的潛力運算架構。

imec表示,透過整合技術和系統級調節策略,在達成AI訓練工作負荷下,GPU的最高溫度可能從140.7°C降到70.8°C—相當於目前的2.5D整合技術。這項研究結果展示結合跨層優化(也就是協同優化在所有不同抽象層上的開關)與廣泛技術專業所帶來的優勢—imec特有的組合。

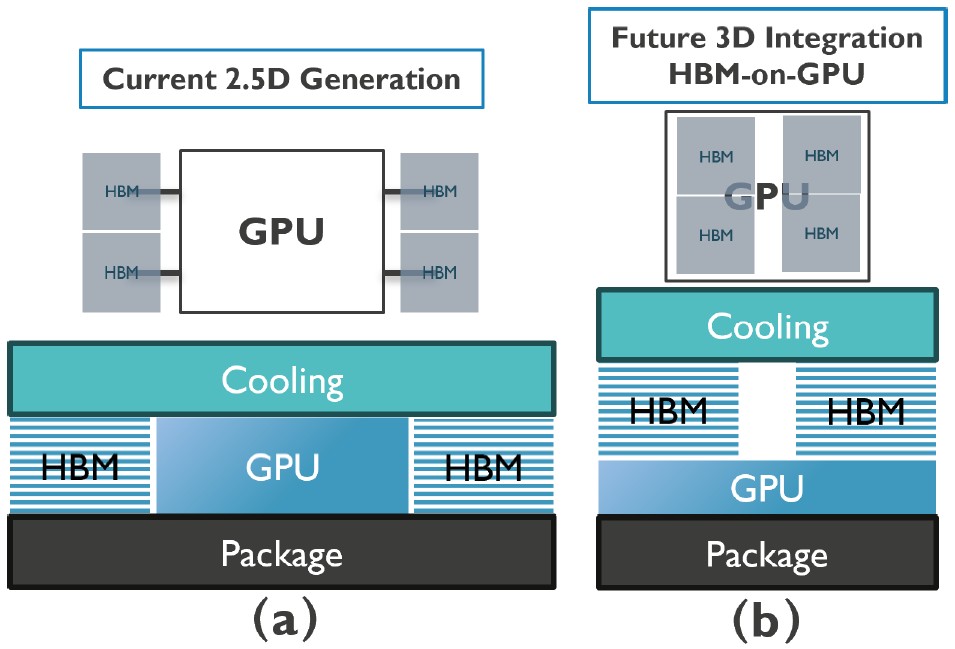

imec指出,直接在GPU上方整合HBM堆疊提供一套具吸引力的方法來建立新一代運算架構,以滿足資料密集型的AI工作負荷。相較於在矽中介層上將HBM堆疊置於(單顆或兩顆)GPU附近的現行2.5D整合技術,這種HBM與GPU堆疊的3D元件可望在運算密度(每封裝包含四顆GPU)、每顆GPU的記憶體容量及GPU記憶體頻寬方面跨出一大步。然而,積極的3D整合方法因為具備更高的局部功率密度及垂直方向的熱阻,因而容易產生散熱問題。

▲整合方法(a)目前的2.5D方案與(b)HBM與GPU堆疊的3D提案。

▲整合方法(a)目前的2.5D方案與(b)HBM與GPU堆疊的3D提案。

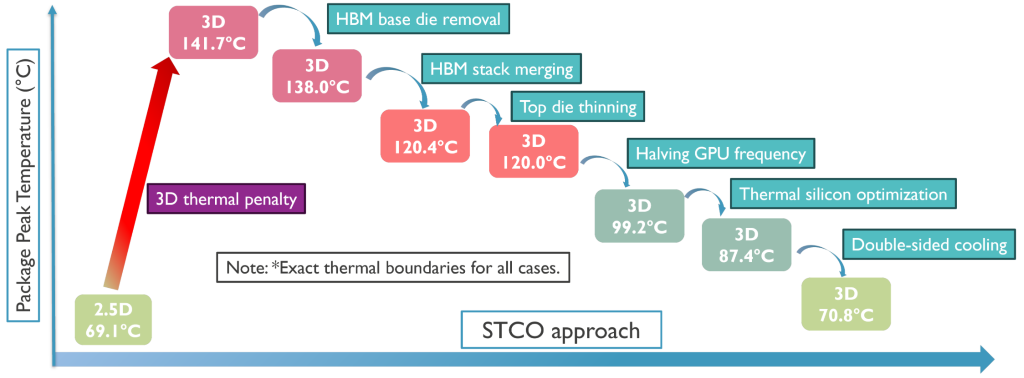

在2025年IEEE國際電子會議,imec發表首篇針對立體HBM與GPU堆疊元件整合的完整熱模擬研究,不僅辨別散熱瓶頸,也提出策略來提升該架構散熱可行性。imec研究人員展示協同優化技術和系統級熱調節方法如何在現實的AI訓練工作負荷下,將GPU最高溫度從141.7°C降到70.8°C。

imec強調,這套模型假設四個HBM堆疊—每堆疊包含12顆異質接合的DRAM晶粒,利用凸塊直接放在GPU上方。散熱位在這些HBM的上方。透過取自產業相關功率曲線的功率圖來識別局部熱點,並與2.5D基線進行比對。不採用熱調節策略時,3D模型產生141.7°C的GPU峰值溫度—遠高於GPU和HBM的運作溫度,而在相同的散熱條件下,2.5整合的基準測試最高溫度落在可維持運作的69.1°C。我們運用這些資料來著手評估技術和系統級熱調節策略兩者所產生的共同影響。系統級策略包含HBM堆疊合併與矽材散熱優化等等。系統級方面,我們評估了雙面降溫與GPU頻率調整的影響。

imec系統技術協同優化(STCO)研究計畫主持人James Myers表示,將GPU核心頻率減半成功把峰值溫度從120°C降到100°C以下,達到記憶體運作的目標。雖然這一步會增加28%的工作負荷,也就是放緩AI訓練步驟,但整體封裝的表現勝過2.5D基線測試,這歸功於3D設置所提供的更高通量密度。我們正在利用這套方法來研究其他GPU/HBM配置,例如把GPU放在HBM上方,以預料未來的熱學限制。

▲採用系統技術協同優化(STCO)的累積熱調節成效。

▲採用系統技術協同優化(STCO)的累積熱調節成效。

imec邏輯晶片技術研發副總Julien Ryckaert表示,這也是我們第一次展示imec跨技術協同優化(XTCO)研究計畫在建立更具備熱穩健度之運算系統的能力。XTCO計畫於2025年展開,目標是促使imec的技術發展途徑與關鍵的業界系統升級挑戰能夠高效密切配合,該計畫也奠基於四大系統級支柱:運算密度、供電、散熱,以及記憶體密度和頻寬。結合了我們的系統技術協同優化(STCO)/設計技術協同優化(DTCO)思維與imec廣泛的技術專業,這種獨特整合在應對運算系統需求的成長及多樣化方面提供寶貴價值。我們邀請整個半導體生態系內的企業加入我們的跨技術協同優化計畫,包含無晶圓廠與系統廠商,並攜手克服關鍵的系統升級瓶頸。

(首圖來源:shutterstock)