矽光子引爆百億商機:

Nvidia、台積電、Broadcom 的下一張王牌

矽光子成為 AI 時代新曙光?

根據研究機構 Epoch AI 數據,近年 AI 模型訓練算力需求每年以 4~5 倍速度成長,遠超過摩爾定律每 18 個月效能增加一倍的速度。半導體巨頭們以 3D 堆疊、異質整合封裝等方式,增加 AI 晶片運算效能,為早已臨界物理極限的摩爾定律續命。二是藉由強化晶片間、伺服器間的串連,來實現規模化運算,提升運算能力。這種規模化分為Scaling Up 與 Scaling Out 兩種策略。

Scaling Up vs. Scaling Out

Scaling Up(垂直擴展)

晶片跟晶片間的串連,透過增加多顆 GPU、TPU 等運算晶片,增加單一伺服器或計算節點的運算能力。

如果說 Scale up 是獨自升級,Scale out 是納入更多的團隊成員群體作戰。在 AI 叢集發展下,這兩種策略高速傳輸都是至關重要。伺服器之間雖然已採用光纖傳輸,透過光收發模組進行電與光訊號轉換,但隨著數據量爆炸成長,傳統光收發模組已面臨傳輸瓶頸與功耗挑戰,矽光子正是在此背景下應運而生。

矽光子是什麼?

矽光子(Silicon photonics, SiPh)簡言之是將分散的光學元件,微縮整合在同一個小晶片上。主要透過光的折射與波導原理,讓光受限於特定路徑中傳導,實現在晶片內進行光訊號的傳輸與處理,加速資料傳輸。

此類晶片屬於積體光路(Photonic Integrated Circuit, PIC),相較於傳統積體電路(Electrical Integrated Circuit, EIC)能實現更高頻寬、更快速度及更低能耗的數據處理。

點擊圓點了解各元件功能 (圖片來源:工研院、科技新報再製)

傳送訊號(由內而外)

ASIC 等主晶片產生的電子訊號 → 進入光調變器轉換為光訊號 → 光訊號經光波導傳輸 → 由多工/解多工器控制光路徑並合併/分離多波長訊號 → 光訊號經耦合器耦合出晶片 → 進入外部光纖傳輸。

矽光子技術演進

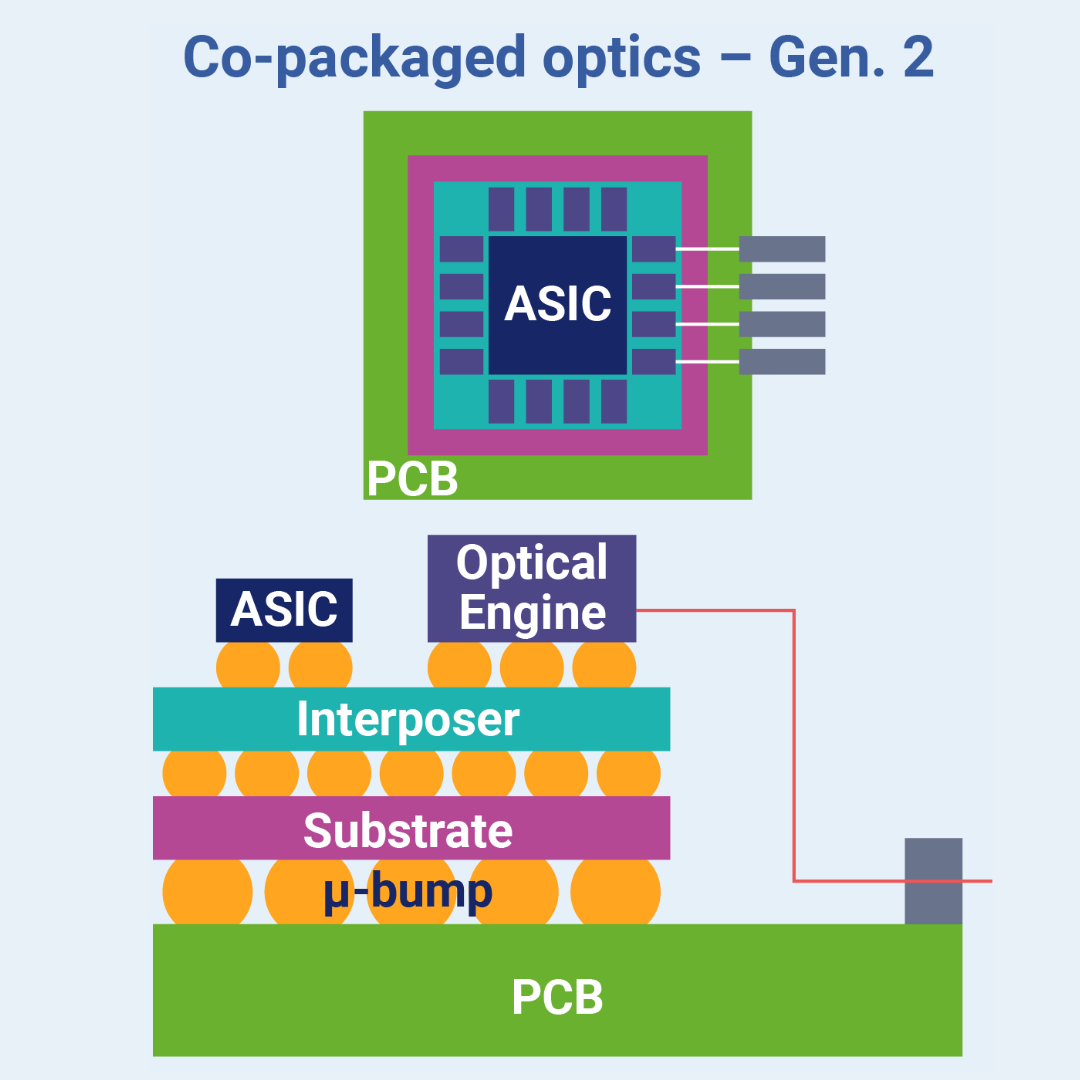

矽光子技術的核心使命在於縮短訊號傳輸路徑,以突破傳統銅線在速度與功耗上的瓶頸。這個演進從最初的傳統可拔插光學模組開始,較長的電路路徑限制了效能。為此,業界發展出LPO(線性可拔插光學)作為過渡,透過簡化電路來降低功耗。然而,最終的技術目標是CPO(共同封裝光學),將光學元件與運算晶片直接共同封裝在同一載板,將傳輸路徑縮至最短。

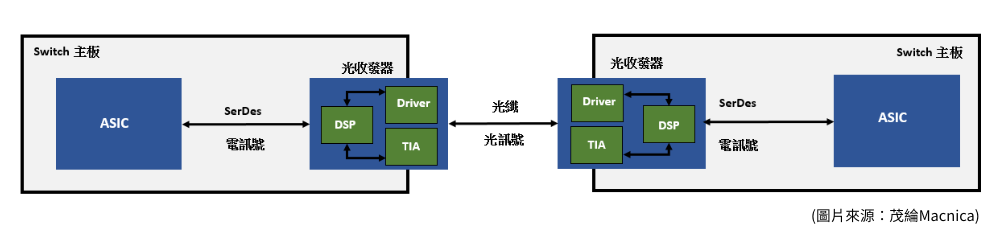

傳統可拔插光收發模組 Pluggable Optics

透過光纖兩端光收發模組轉換電光訊號,再傳遞到 ASIC 等主晶片,隨著大量資料傳輸,面臨傳輸通道不足、高功耗等問題。

CPO 過渡方案演進

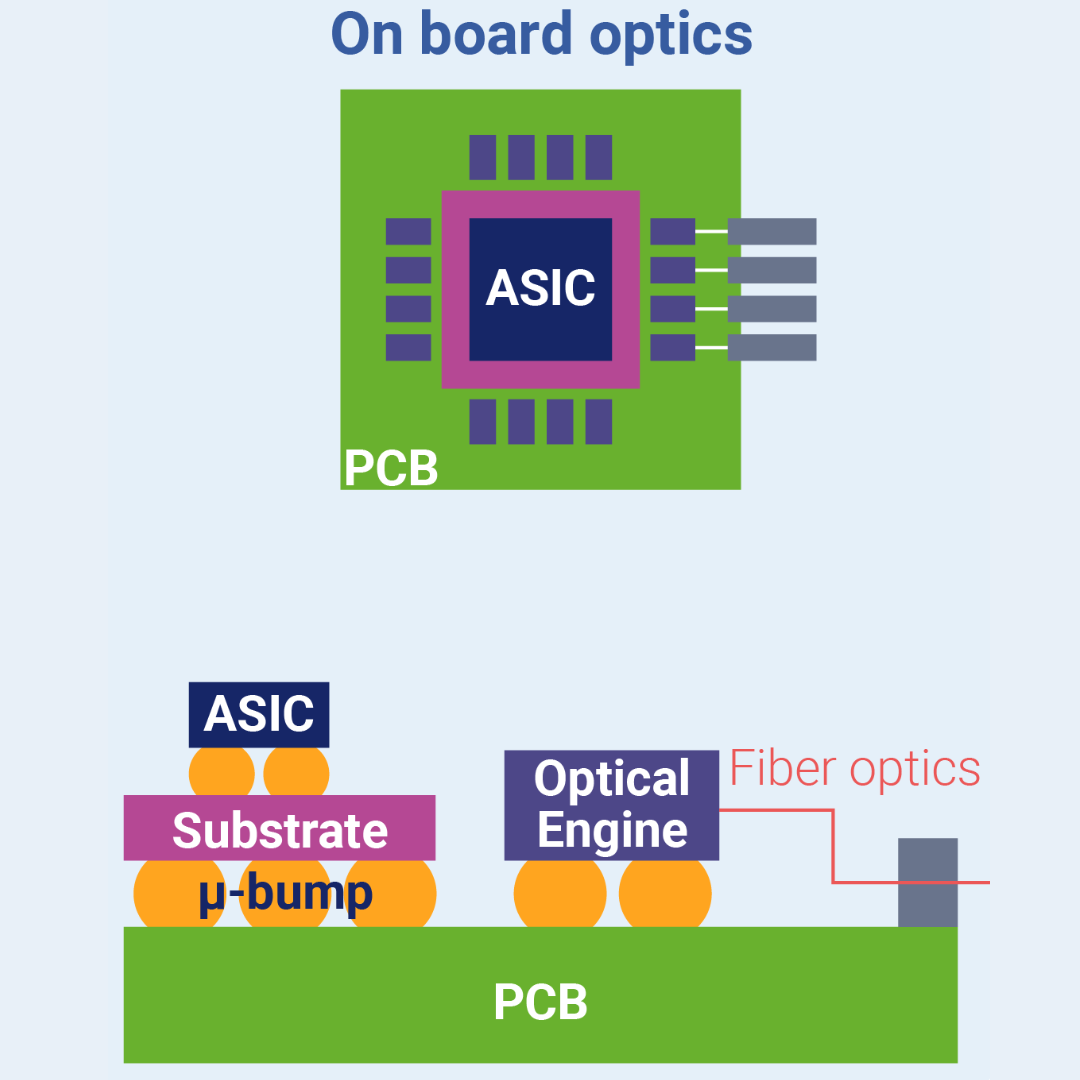

要將光路與電路元件共同封裝,跨材料異質整合難度極高,散熱、可靠度、測試等,尚有種種挑戰待克服,目前 CPO 還未真正商用,CPO 陣營持續發展各種過渡方案,OBO 載板光學封裝(On-Board Optics)是將光模組放在電路板上,安裝在 ASIC 晶片周圍,能夠支援1.6Tbps傳輸速率,已量產。NPO 近封裝光學(Near-Packaged Optics)則透過中介層,逐步減少銅線傳輸比例,推近光模組與運算晶片 ASIC 之間的距離。

OBO

載板光學封裝 (On Board Optics)

將光模組移到伺服器內 PCB 載板,置於 ASIC 晶片周圍。

頻寬:<1.6T

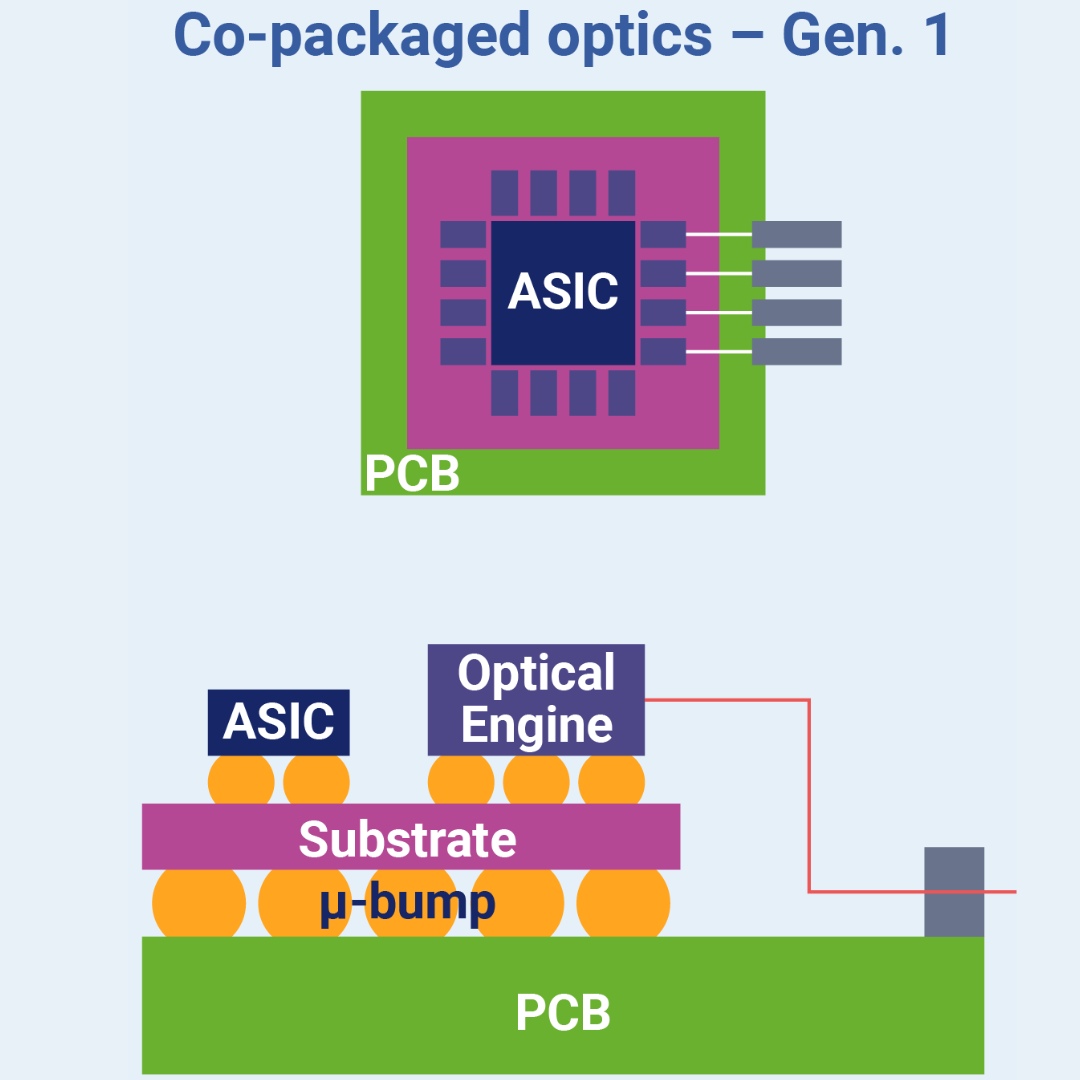

NPO

近封裝光學 (Near-Packaged Optics)

ASIC 與光模組共用基板(substrate),透過導線或走線連結。

頻寬:<3.2T

CPO

共同封裝光學 (Co-packaged Optics)

ASIC 與光模組直接共同封裝。

頻寬:6.4T~

(圖片來源:IDTechEx)

大廠進展與供應鏈

半導體巨頭與相關供應鏈廠商都積極推動矽光子技術,在台積電及日月光倡議下,2024 年國際半導體產業協會(SEMI)與工研院及30多家業者組成矽光子產業聯盟,涵蓋半導體製造、封測、IC 設計、光通訊、面板、系統製造等廠商參與,積極發展矽光子技術。

國際半導體協會(SEMI)預估,2030 年全球矽光子半導體市場規模將達到 78.6 億美元,年複合成長率(CAGR)高達 25.7%。在未來不久將可看到這項技術逐步開花結果。

| 公司 | 技術進展 |

|---|---|

| Nvidia | 與台積電共同研發矽光子技術,預計 2025 年下半、2026 年推出 Spectrum-X Photonics 和 Quantum-X Photonics 矽光子網路交換器,每連接埠數據傳輸速度提升至 1.6 Tb/s,下世代 GPU Rubin 架構將導入矽光子,功耗效率可提升 3.5 倍。 |

| Broadcom | 2025 年 5 月推出第三代 CPO 產品,支援單通道 200G 傳輸速率,第四代 CPO 產品持續研發,目標實現單通道 400G 傳輸速率。 |

| TSMC | 積極發展緊湊型通用光子引擎(Compact Universal Photonic Engine, COUPE)技術,2025 年預期完成小型插拔式連接器的 COUPE 驗證,達成 1.6 Tb/s 傳輸速度;2026 年整合 CoWoS 封裝成為 CPO,將光連結導入封裝中,傳輸速度預期提升四倍。 |

| Intel | 矽光子技術先行者,2010 年就已發展相關技術,但近年較無大規模量產時程消息,2023 年將可插拔矽光學收發器模組業務賣給美國電子零件製造商捷普(Jabil)。 |

| GlobalFoundries | 2025 年初宣布投資 5.75 億美元,在紐約馬爾他廠新設 1 座半導體廠區,用於拓展矽光子產能。 |

供應鏈清單

(來源:券商整理)