上一篇文章首先介紹了降低晶片功耗的重要性,並指出降低晶片工作電壓是有效的方法。接著,介紹了堆疊奈米片的技術,堆疊奈米片是一種新型的電晶體架構,具有比傳統鰭式電晶體更好的效能和功耗表現,將是晶片發展的重要方向。(本文出自國立臺灣大學電子工程學研究所劉致為特聘/講座教授以及其研究團隊,經科技新報編修為上下兩篇,此篇為下篇。)

高介電係數介電層對驅動電流的影響

為了提升電晶體驅動電流,除了提升通道之堆疊層數,增加閘極堆疊 (gate stack) 中的介電層之介電係數也可有效增加驅動電流,同時減少通道堆疊數目來降低製程之難度。採用電漿輔助原子層沉積 (PEALD) HfxZryO2 介電層,通過優化 Hf 和 Zr 濃度以達到高介電係數。

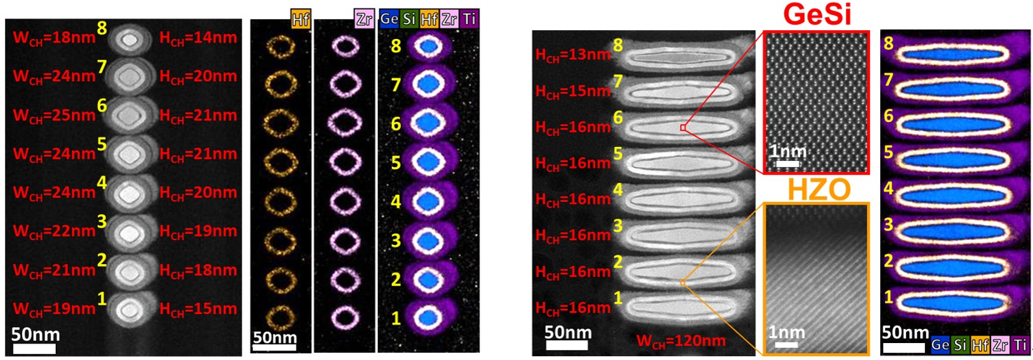

本研究團隊成功整合 Hf0.2Zr0.8O2 高介電係數 (κ=47) 介電層於八層堆疊 Ge0.95Si0.05 nanowires (圖六左) 與 nanosheets (圖六右),其研究成果發表於 2023 VLSI [11]。Nanowires 與 nanosheets 在 VOV=VDS=0.5V 時分別具有 9200μA/μm per footprint 與 360μA per stack 之驅動電流 ( nanosheets 擁有紀錄之驅動電流)。此外透過模擬確認 HZO在[Zr]=80% 可擁有介電係數之峰值,並模擬驗證高介電係數閘極堆疊結合高層數堆疊通道能有效降低閘遲延 (gate delay)。

▲ 圖六:本研究團隊發表之整合 Hf2Zr0.8O2 高介電係數介電層於(左)八層堆疊 Ge0.95Si0.05 nanowires。(右)八層堆疊 Ge0.95Si0.05 nanosheets [11]。© 2023 JSAP

二維材料在電晶體應用上的挑戰

鍺矽 (GeSi)、鍺 (Ge)、鍺錫 (GeSn) 等鍺基材料,具有優於矽的載子遷移率,可增加電晶體的驅動電流,並且與現今業界的矽半導體製程技術有良好的相容性,具有成為下世代通道材料的潛力。其他非矽基的新穎材料,例如氧化物半導體 (Oxide Semiconductor) 與二維材料 (2D material),作為電晶體通道使用的研究近年來大幅展開。二維材料由於單層原子的特性,許多人對其微縮的潛力高度期待,在 Nature、IEDM、VLSI 上皆有相關的論文探討。

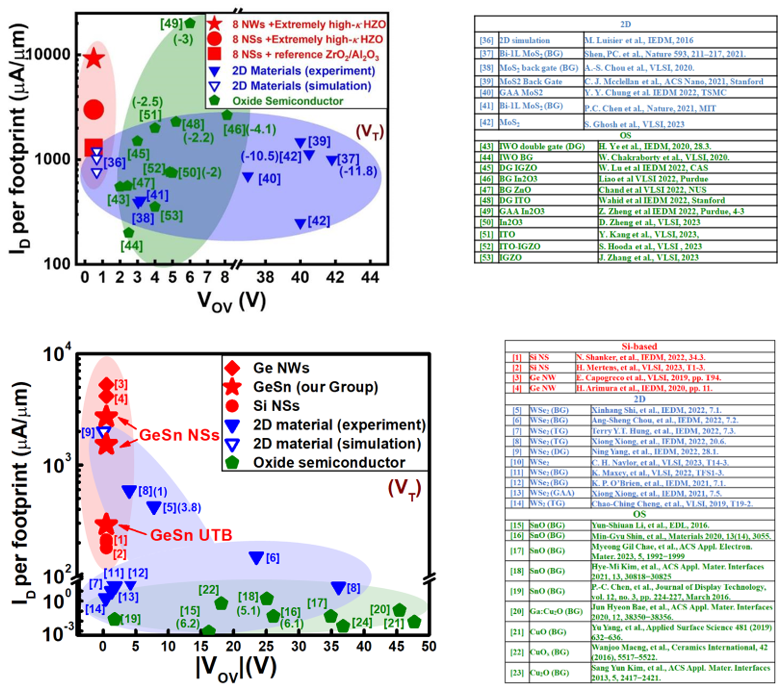

然而,二維材料面臨了大面積高品質的晶圓成長技術挑戰,以及高接觸電阻、低電流等諸多問題。二維材料在元件製程上難與業界成熟之矽基材料相容,在元件效能的表現上也較四族材料電晶體有差距。對於 n 型電晶體而言,許多氧化物半導體與二維材料電晶體呈現負的 threshold voltage (VT) 以及相當大的 overdrive voltage (VOV) (圖七上) [12],是無法應用於先進 IC 當中的。此外對於p型電晶體而言,大多氧化物半導體與二維材料電晶體仍呈現相當大的 VOV,同樣難以應用於先進 IC 當中(圖七下)。相較於氧化物半導體與二維材料,四族材料在低 VOV 的條件下仍然可以擁有較高的驅動電流。

▲ 圖七:四族材料、氧化物半導體及二維材料之(上) n 型電晶體[12] © IEEE 與(下) p 型電晶體之電流與 VOV 比較圖。

互補式堆疊電晶體對運算效能的提升

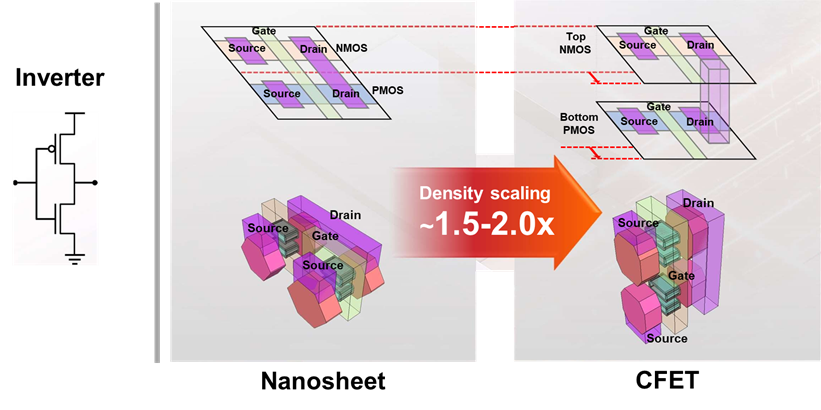

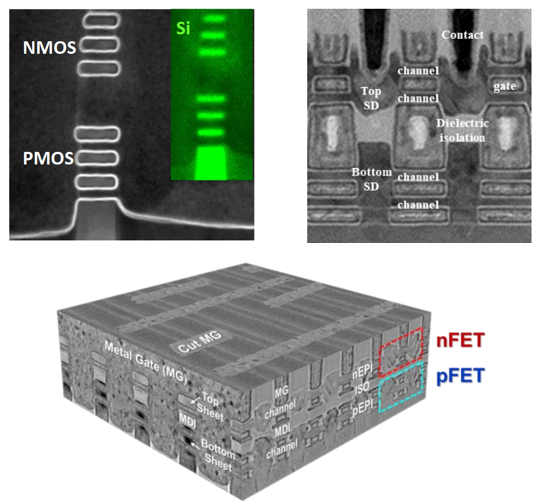

根據 IMEC 的元件藍圖(圖四) [2],在 A5 技術節點 (2032年) 引入互補式堆疊電晶體 (CFET)。互補式堆疊電晶體比起水平擺放的電晶體可以減少反相器 (inverter) 單元的佔地面積,最大可將反相器單元面積縮減至一半(圖八) [4],可提升單位面積內的電晶體數目,增加運算效能,持續推進技術節點,成為研究上的重要題目。業界也積極開發互補式堆疊電晶體,為接替堆疊奈米片的下一個電晶體架構做準備。在 2023 IEDM 中,Intel (圖九上左) [13]、Samsung (圖九上右) [14]以及台積電(圖九下) [15]皆發表在互補式堆疊電晶體的研究發展成果。

▲ 圖八:互補式堆疊電晶體示意圖,進一步減少反相器單元的佔地面積(最多可減少至原先面積的一半) [4]。© IEEE

▲ 圖九:(上左 )Intel 發表之互補式堆疊電晶體[13]。© IEEE

(上右) Samsung 發表之互補式堆疊電晶體[14]。© IEEE

(下)台積電發表之互補式堆疊電晶體[15]。© IEEE

多層 P/N 接面作為電性隔絕的優勢

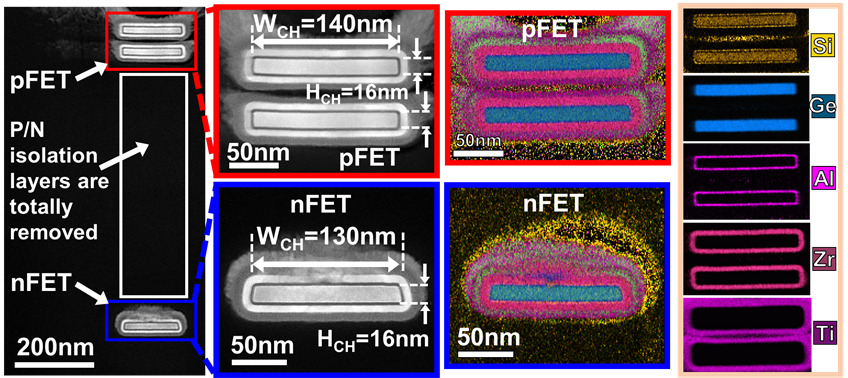

本研究團隊成功將 n 型與 p 型奈米片電晶體進行垂直方向的堆疊(圖十),並且組成反相器結構成功量測反相器特性。藉由三維單晶片整合 (3D monolithic stacking),透過磊晶成長底層電晶體之通道層、中間之犧牲層以及上層電晶體之通道層,過程中不需要晶圓接合 (wafer bonding),簡化製程複雜度並降低晶圓成本,利用高遷移率鍺矽通道作為互補式堆疊電晶體中之 n 型與 p 型奈米片以提高效能。

在電晶體堆疊的結構中,電晶體之間良好的絕緣 (isolation) 才能確保電晶體各自能夠獨立操作而不會互相影響。本研究團隊採用多層P/N 接面作為堆疊電晶體之間的電性隔絕,不需要複雜的源極/汲極再生長 (S/D regrowth) 製程,並且能夠取代絕緣層沉積,化簡元件製作流程。相關成果已發表於 2022 IEDM 國際研討會[16]。

▲ 圖十:本研究團隊發表之鍺矽通道互補式堆疊電晶體,將 p 型奈米片電晶體垂直堆疊於 n 型奈米片電晶體之上構成反相器單元[16]。© IEEE

異質鍺錫與鍺矽通道之整合技術

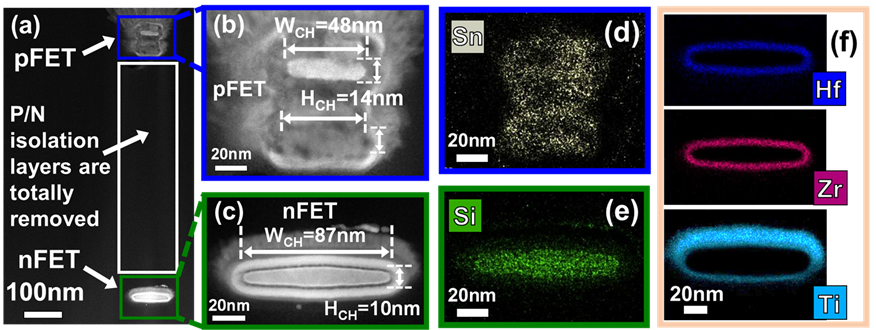

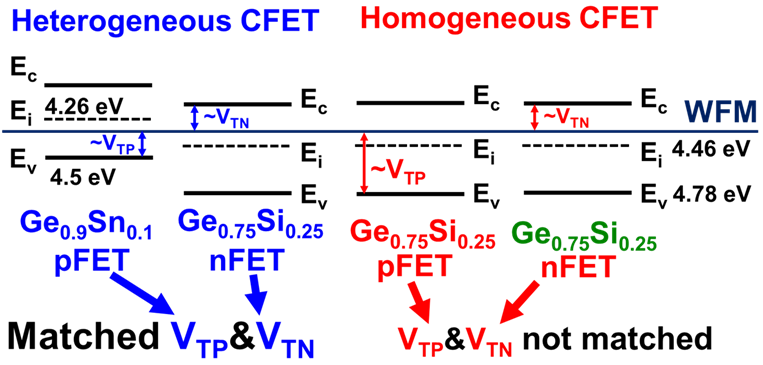

本研究團隊基於單晶片互補式堆疊電晶體結構開發經驗,進一步強化製程,達成世界首顆單晶片堆疊整合異質鍺錫與鍺矽奈米片之互補式堆疊電晶體 (圖十一)。透過磊晶成長底層鍺矽奈米片電晶體之通道層、中間之犧牲層以及上層鍺錫奈米片電晶體之通道層,過程中不需要晶圓接合即可達成異質鍺錫與鍺矽通道之整合。藉由鍺錫與鍺矽通道之間的能帶偏移 (band alignment),僅使用單一種金屬功函數閘極堆疊即完成 VT 匹配的反相器 (圖十二),無須採用高深寬比雙金屬功函數閘極堆疊之複雜製程。

異質鍺錫與鍺矽通道互補式堆疊電晶體相較於 VT 不匹配的鍺矽通道互補式堆疊電晶體能夠擁有更好的反相器特性。此外也整合高介電常數之 Hf0.2Zr0.8O2 閘極介電層,能有效提升互補式堆疊電晶體之效能。相關成果已發表於 2023 IEDM 國際研討會[17]。

▲ 圖十一:本研究團隊發表的異質鍺錫與鍺矽通道互補式堆疊電晶體,成功將 p 型鍺錫奈米片垂直堆疊於 n 型鍺矽奈米片之上並構成反相器單元[17]。© IEEE

▲ 圖十二:藉由異質鍺錫與鍺矽通道之間的能帶偏移可完成 VT 匹配之反相器[17]。© IEEE

依照現有的研發狀況,二維材料要取代矽基,成為主流技術,仍需要很多很多的努力。

延伸閱讀:

References:

[1] Jin Cai, “CMOS Device Technology For the Next Decade,” IEEE Symposia on VLSI Technology and Circuits (VLSI), SC1-1, 2021.

[2] “20-year semiconductor roadmap” [Online] https://www.imec-int.com/en/articles/20-year-roadmap-tearing-down-walls

[3] G. Yeap et al., “5nm CMOS Production Technology Platform featuring full-fledged EUV, and High Mobility Channel FinFETs with densest 0.021μm2 SRAM cells for Mobile SoC and High Performance Computing Applications,” IEEE International Electron Devices Meeting (IEDM), pp. 879-882, 2019.

[4] Y. -J. Mii, “Semiconductor Innovations, from Device to System," 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2022, pp. 276-281.

[5] “Intel Accelerated” [Online] https://download.intel.com/newsroom/2021/client-computing/Intel-Accelerated-2021-presentation.pdf

[6] Mark Liu, “Unleashing the Future of Innovation,” 2021 IEEE International Solid-State Circuits Conference (ISSCC), Plenary Session 1.1, 2021.

[7] S. Barraud et al., “7-Levels-Stacked Nanosheet GAA Transistors for High Performance Computing,” IEEE Symposia on VLSI Technology and Circuits (VLSI), TC1.2, 2020.

[8] Y.-C. Liu et al., “First Highly Stacked Ge0.95Si0.05 nGAAFETs with Record ION = 110 μA (4100 μA/μm) at VOV=VDS=0.5V and High Gm,max = 340 μS (13000 μS/μm) at VDS=0.5V by Wet Etching,” IEEE Symposia on VLSI Technology and Circuits (VLSI), T15-2, 2021.

[9] S. Thomas, “Germanium nanowire transistors stack up,” Nature Electronics, Vol. 4, July 2021, 452.

[10] Y.-R. Chen et al., “Fabrication and performance of highly stacked GeSi nanowire field effect transistors,” Communications Engineering, 2, 77, 2023.

[11] Y.-C. Liu et al., “Extremely High-k Hf0.2Zr0.8O2 Gate Stacks Integrated into Ge0.95Si0.05 Nanowire and Nanosheet nFETs Featuring Respective Record ION per Footprint of 9200μA/μm and Record ION per Stack of 360μA at VOV=VDS=0.5V,” IEEE Symposia on VLSI Technology and Circuits (VLSI), T16-4, 2023.

[12] W.-J. Chen et al., “Extremely High-κ Hf0.2Zr0.8O2 Gate Stacks Integrated Into Eight Stacked Ge0.95Si0.05 Nanowires and Nanosheets nFETs to Boost ION,” IEEE Transactions on Electron Devices, 70, 12, 2023.

[13] M. Radosavljević et al., “Demonstration of a Stacked CMOS Inverter at 60nm Gate Pitch with Power Via and Direct Backside Device Contacts,” IEEE International Electron Devices Meeting (IEDM), 29-2, 2023.

[14] J. Park et al., “First demonstration of 3-dimensional stacked FET with top/bottom source-drain isolation and stacked n/p metal gate,” IEEE International Electron Devices Meeting (IEDM), 29-4, 2023.

[15] S. Liao et al., “Complementary Field-Effect Transistor (CFET) Demonstration at 48nm Gate Pitch for Future Logic Technology Scaling,” IEEE International Electron Devices Meeting (IEDM), 29-6, 2023.

[16] C.-T. Tu et al., “First Demonstration of Monolithic 3D Self-aligned GeSi Channel and Common Gate Complementary FETs by CVD Epitaxy Using Multiple P/N Junction Isolation,” IEEE International Electron Devices Meeting (IEDM), pp.479-482, 2022.

[17] C.-T. Tu et al., “First Demonstration of Monolithic Self-aligned Heterogeneous Nanosheet Channel Complementary FETs with Matched VT by Band Alignments of Individual Channels,” IEEE International Electron Devices Meeting (IEDM), 29-5, 2023.

(首圖來源:Shutterstock;資料來源:本篇文章由國立臺灣大學電子工程學研究所劉致為特聘/講座教授提供,科技新報修編)