AI 算力競賽持續升溫,GPU 運算叢集規模從「千卡」擴大到「萬卡」、甚至「十萬卡」等級,晶片間資料傳輸需求呈指數成長。當傳輸速率提升至 800G、1.6T,傳統銅線電訊號互連逐漸逼近物理極限,加速矽光子(SiPh)光互連相關技術發展。其中,將光學引擎與運算晶片共同封裝的 CPO,被視為下一代 AI 基礎設施布建關鍵。輝達執行長黃仁勳更將 2026 年定調為矽光子商轉元年,而這場光電整合革命背後,先進封裝技術扮演了關鍵角色。

矽光子是將光調變器、光電二極體等光學元件透過 CMOS 製程整合於矽晶片,使光子積體電路(PIC)與電子積體電路(EIC)能在同一系統協同運作。進一步發展的 CPO(Co-Packaged Optics) 期望將上述光學引擎直接與 ASIC 或運算晶片共同封裝,將原本數十公分的銅線傳輸距離縮短至毫米等級,以降低功耗並提升高速資料傳輸效率。

理想豐滿現實卻很骨感,儘管矽光子、CPO 概念發展多年,但仍走得緩慢,背後最難克服的是在封裝技術上的重重挑戰。材質不同的光(PIC)與電(EIC)必須在極小空間內完成高密度互連,同時還有光學耦合、封裝翹曲、散熱等種種複雜問題。

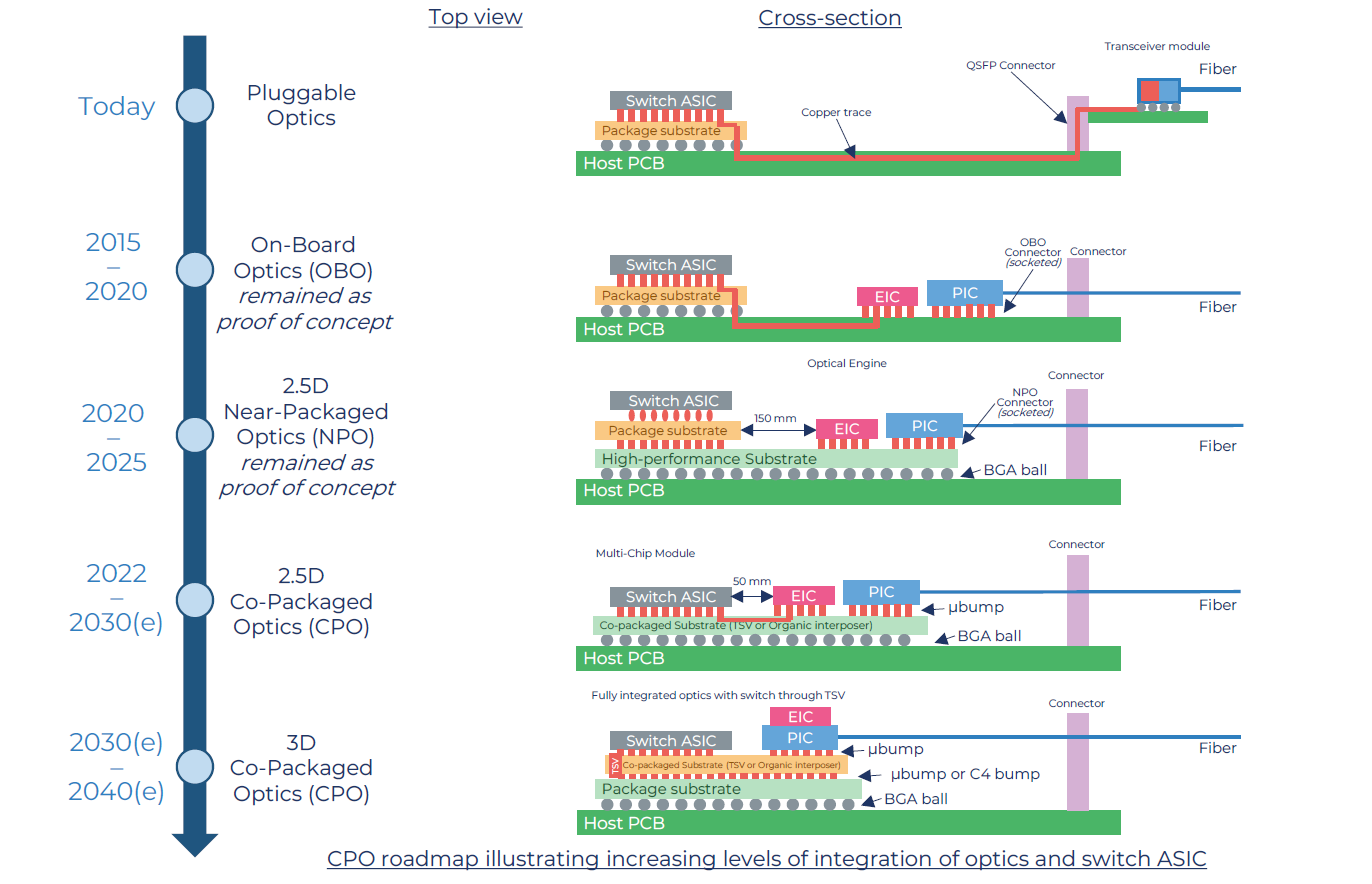

▲ 矽光子概念發展多年,但市場預期結合 2.5D、3D 封裝,ASIC 運算晶片與光學引擎(PIC+EIC)共同封裝的 CPO 技術,要到 2030 年左右才有望真正普及。(Source:Yole)

從 2D 到 3D,先進封裝如何推動矽光子發展

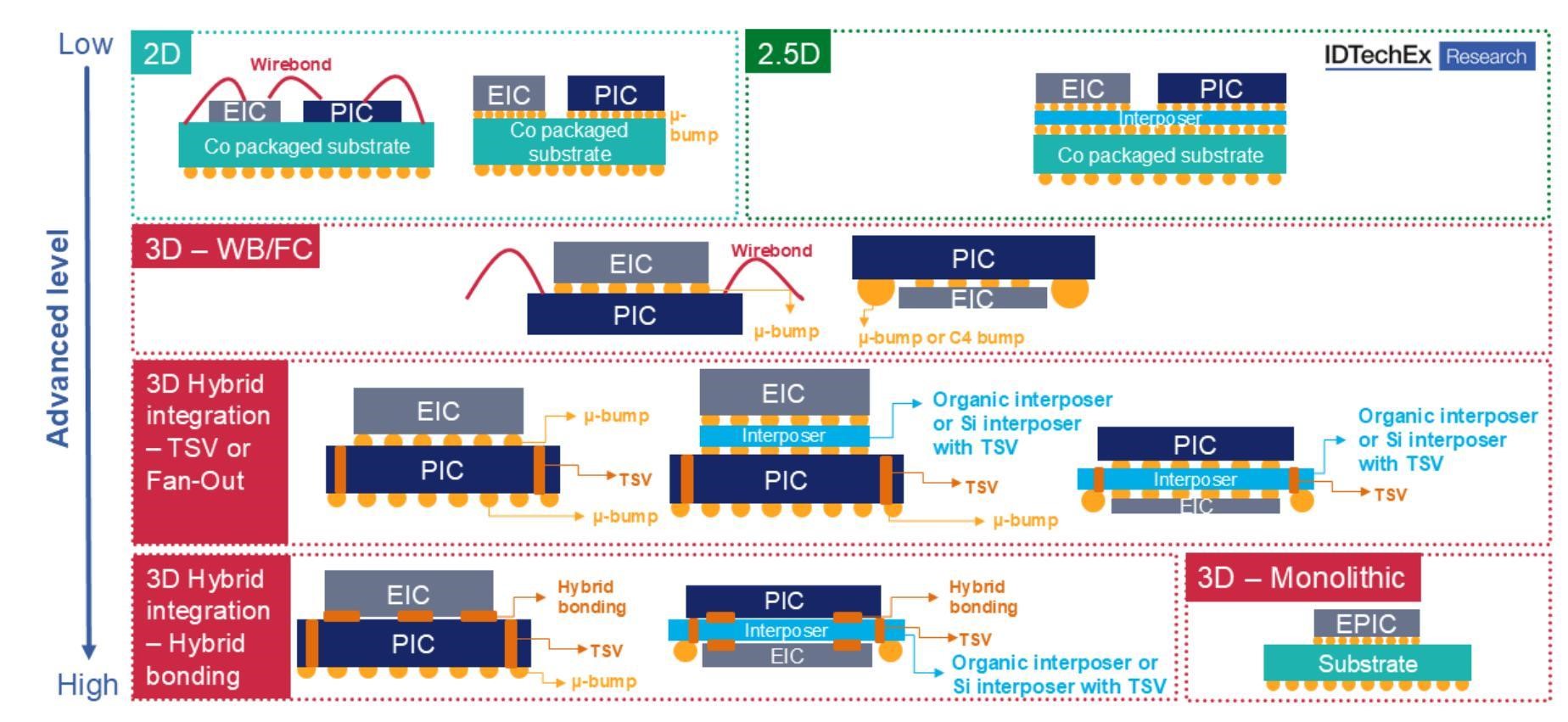

光子積體電路(PIC)與電子積體電路( EIC)的互連封裝,從早期 2D 打線接合封裝(Wire Bonding),兩顆晶片並排置於同個基板連接,訊號傳輸距離較長且容易產生寄生效應。進階到 2.5D 封裝,將 PIC、EIC 一同堆疊於矽中介層,透過單晶片整合提高連接密度與訊號效率,在寄生效應、訊號延遲與功耗表現上有更佳的表現,然而,建構 PIC 的矽光子(SiPh) 製程,通常只需 35 奈米以上製程節點,PIC、EIC 單晶片的整合實則限制了 EIC 的性能。

先進封裝 3D 異質整合的進步,利用矽穿孔(TSV)、混合鍵合(Hybrid Bonding)等技術,讓 PIC、EIC 得以用不同製程垂直堆疊整合,同時大幅縮短互連距離、降低功耗。先進封裝技術的每一次突破,也逐步在推動矽光子的發展。

而這當中具備先進封裝技術能力的晶圓代工、封測廠在矽光子發展中角色越發重要,其中台積電、日月光正逐漸成為 CPO 生態系的重要推手。

▲ 光學引擎封裝技術圖,從 2D 封裝到 2.5D、3D 封裝 TSV與混合鍵合等封裝技術進展,使光子晶片(PIC)與電子晶片(EIC)得以逐步縮短互連距離。(Source:IDTechEx)

台積電 COUPE 在矽光子領域的彎道超車

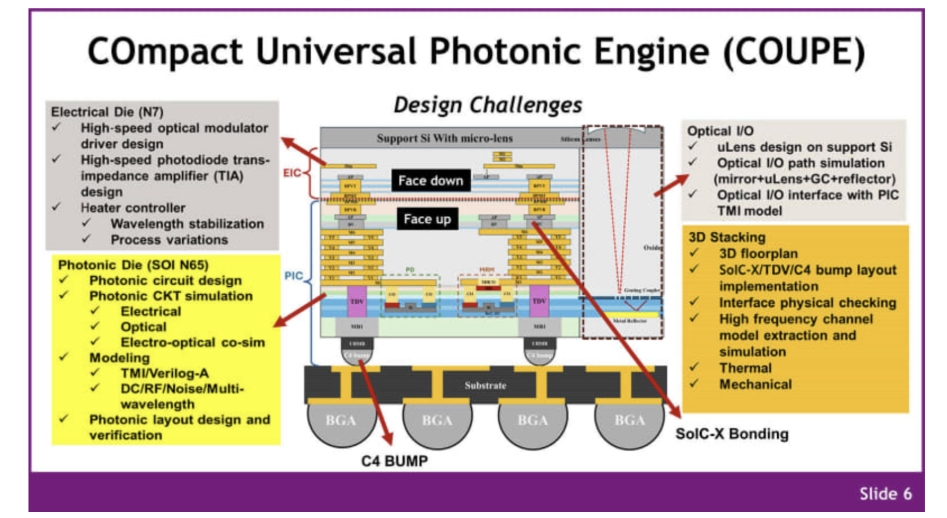

晶圓代工廠商相較於格羅方德與高塔半導體較早進入矽光子市場,台積電雖布局較晚,但跳過單一晶片封裝(Single Die),結合先進封裝優勢,提出 COUPE(Compact Universal Photonic Engine)直接透過 3D 封裝 SoIC-X 技術,連接不同製程的光子積體電路(PIC)與電子積體電路(EIC)。

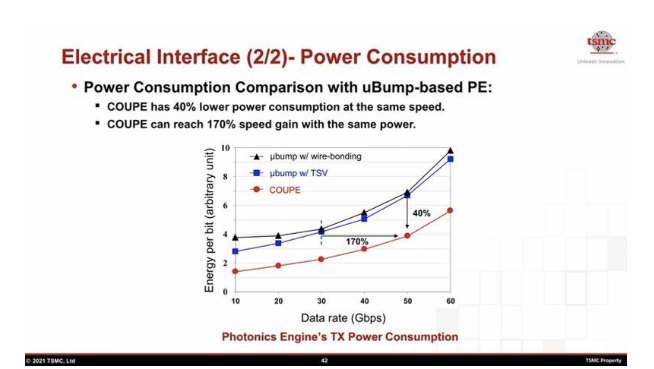

SoIC 以混合鍵合方式銅對銅直接做晶片間的連接,SoIC-X 省去凸塊(bumpless)讓晶片之間連接更緊密。根據台積電數據,相較於微凸塊(uBump)技術,混合鍵合在相同速度下可降低 40% 功耗,或在相同功耗下達到 170% 速度提升。

(Source:台積電)

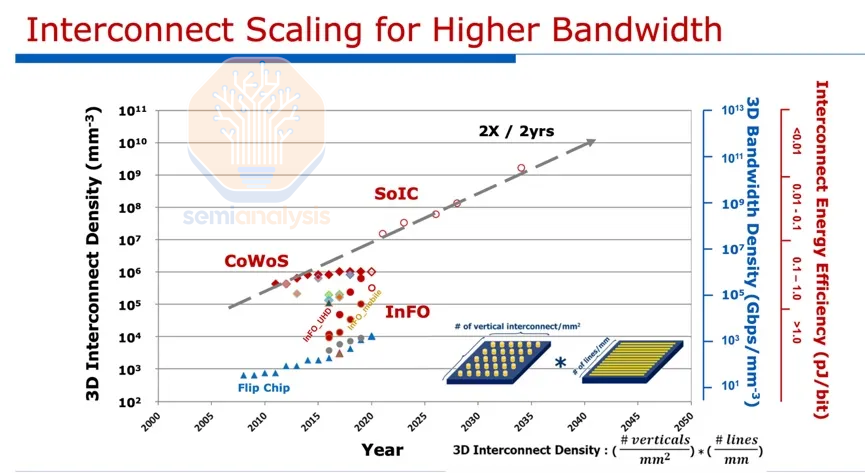

以下圖為例,互連密度的提升相對應提升頻寬,同時降低互連能校(Interconnect Energy Efficiency),Flip-Chip 每位元傳輸功耗大於 1.0 pJ/bit,而 SoIC 能使功耗大幅降至 0.1 pJ/bit 以下。隨著 AI 高速光互連市場對高頻寬、低功耗的需求提高,也說明台積電為何以 SoIC-X 切入矽光子封裝市場。

▲ SoIC 相較 CoWoS、InFO 等封裝技術,晶片互連密度更高,在高頻寬、低功耗擁有更佳的優勢。(Source:semianalysis)

從日本媒體 INTERNET Watch 揭露的台積電 2025 年 VLSI 技術及電路研討會簡報,COUPE 上層 EIC 採用 N7 較先進 CMOS 製程,整合光學調變驅動器、轉阻放大器(TIA)與波長控制用的熱調節器;下層 PIC 則為較成熟 N65 SOI 製程,整合調變器(modulator)、波導(Waveguide)等光學元件。兩者透過 SoIC-X 3D 堆疊,實現小於 10 微米的互連間距、降低電阻與寄生電容。

COUPE 同時包含完整的製程設計套件(PDK),支援光子電路設計、電光協同模擬與多波長建模,包含光學介面也發展出垂直的光柵耦合(Grating Coupler, GC)與水平的邊緣耦合(Edging Coupler, EC)兩種解決方案,來提升與光纖陣列模組(FAU)的光耦合效率。

目前光柵耦合技術因耦合耗損較低穩定性較高,也被視為主要先行採用的解決方案,再同時搭配矽基微透鏡(uLens)、電介質通孔(TDV)、金屬反射層與抗反射塗層等結構設計控制光學輸出。包含台積電與 Nvidia 的合作都是採光柵耦合,而原先採取邊緣耦合的博通,市場推測與台積電 COUPE 合作可能也轉向光柵耦合。

▲ 實際運作流程中,外部訊號先透過矽穿孔(TSV)進入 PIC 並直通上方 EIC 進行處理。EIC 將數位訊號轉為光調變訊號後,再經由 TSV 回傳至下層 PIC 的微環共振器(MRM)。最終,受調變的光訊號通過波導與光柵耦合器,並由下方的金屬反射鏡與上方的矽基微透鏡精準匯聚,高效耦合至光纖輸出。(Source:INTERNET watch)

COUPE 大幅縮小了光學引擎(OE)體積,得以讓更多光引擎緊鄰交換器 ASIC,為未來與運算晶片共封裝鋪路,台積電在矽光子發展中的角色也愈發重要,關鍵在於 COUPE 與 CoWoS 的整合,當前 AI 加速器幾乎全面採用 CoWoS,未來光互連若要導入 GPU 或 AI ASIC 封裝,就必須與 CoWoS 架構協同設計。COUPE 正是以此為目標打造,台積電 2025 年已完成 COUPE 可拔插收發模組驗證,傳輸速率達 1.6 Tbps,2026 年 COUPE 光引擎與 CoWoS 製程 ASIC 整合在基板,傳輸速率達 6.4 Tbps,最終再逐步朝 GPU 與光引擎共封裝的 Optical I/O 演進。

從 TSV 到 FOPoP,日月光布局矽光子 3D 封裝

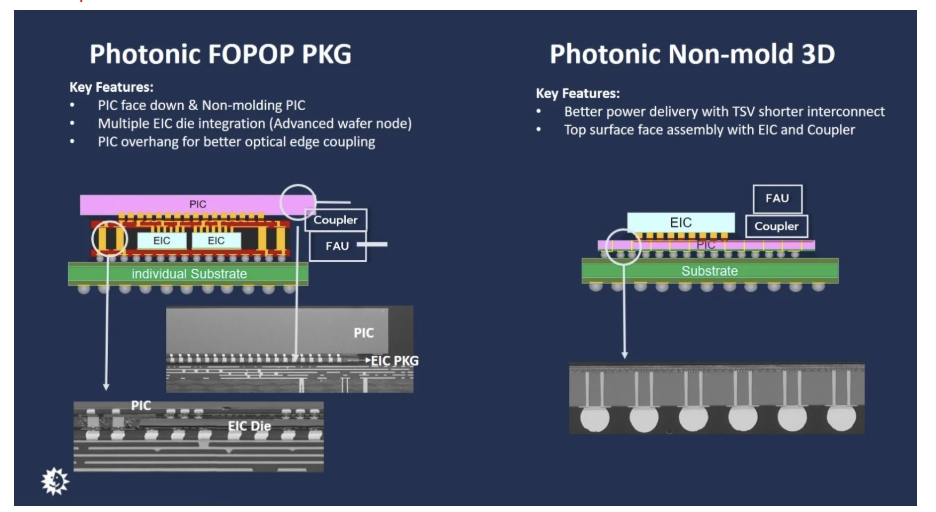

針對矽光子 3D 封裝,日月光在其技術部落格則提出透過矽穿孔(TSV)或以扇出型堆疊封裝(Fan-Out-Package-on-Package,FOPoP)高銅柱(copper pillars)互連兩大技術路徑,來實現光子積體電路(PIC)與電子積體電路(EIC)的垂直互連。

Non-mold 3D 主要將 PIC 置於下方,並使用 PIC 形成的 TSV 與放上方的 EIC 進行垂直互連,PIC 上方、EIC 旁邊整合耦合器(coupler)與光纖陣列模組(FAU)與外部光纖光源耦合。FOPoP 方案則將 PIC 置於 EIC 上方,再利用扇出區以銅柱互連,而銅柱間懸空的部分允許邊緣耦合(Edging Coupler, EC)。日月光整合於 VIPack 平台的 FOPoP 技術,可將電氣路徑減少 3 倍,頻寬密度提高 8 倍,使引擎頻寬擴展每單位達到 6.4 Tbps。

2025 年 4 月日月光展示 CPO 相關解決方案,已可將多個光學引擎(OE)與 ASIC 晶片直接整合在單一封裝內,實現小於 5 pJ/bit 功耗並且大幅增長帶寬,大幅降低過往可拔插光學模組20~30 pJ/bit 的功耗。

(Source:日月光)

投資機構 Bernstein 分析日月光/矽品在矽光子能提供的服務包含:利用 VIPack 平台做 PIC 與 EIC 封裝、提供 PIC/EIC 與 ASIC 交換機晶片封裝,以及為整個 CPO 晶片提供系統級封裝(Sip)。

AI 網路交換器進入矽光子新時代

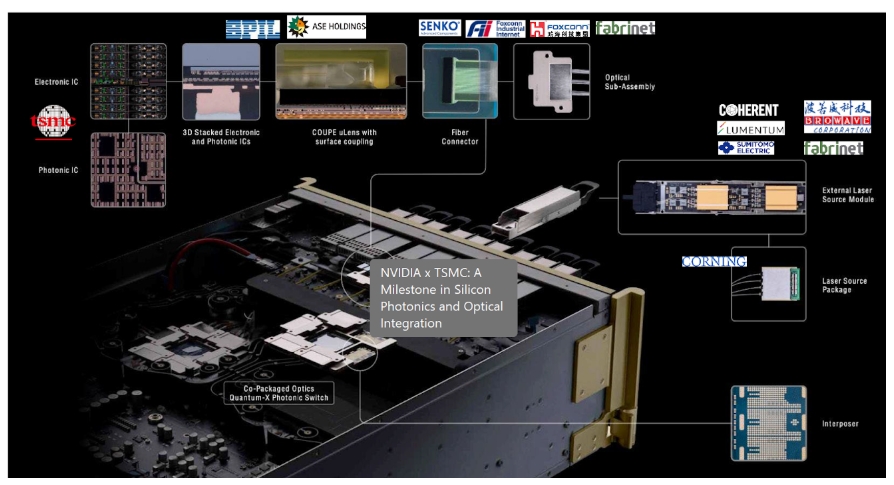

在先進封裝技術助攻下,AI 資料中心網路頻寬也開始邁入新世代。早已推出矽光子晶片的博通,在 2025 年 10 月推出新一代 Tomahawk 6-Davisson CPO 交換器,轉向台積電 COUPE 封裝,晶片交換容量達到 102.4 Tbps,較現有乙太網路交換器頻寬的兩倍。

同時間,輝達首款採用矽光子技術的 Quantum-X800 InfiniBand 交換器,總頻寬達 115.2 Tbp量產,而 Spectrum-X800 乙太網路交換器預計於 2026 年問世,預期將光學引擎整合進 CoWoS 封裝中。兩者背後所採用的同樣是台積電 COUPE 封裝解決方案。

從 Quantum-X800 供應鏈拆解來看,EIC 與 PIC 光學引擎由台積電 COUPE 整合,再由日月光/矽品進行後段封裝,涵蓋關鍵的光學介面耦合與光纖對準。

(Source:Yole)

摩根士丹利(Morgan Stanley)指出,台積電目前 PIC 月產能約 500 片,預期在客戶積極擴產下,2027 年第一季月產能將達到1 萬片。摩根士丹利預期,2026 年 CPO 交換器出貨約 2.3 萬台,其中主要以輝達 100T 交換器晶片 Spectrum 佔最大市場份額。根據目前樂觀情況 2027 年將達到 5.9 萬台,預估到 2030 年將達到 20 萬台,2024 年到 2030 年年複合成長率(CAGR)預期高達 144%。

儘管矽光子已開始邁入商轉階段,但 CPO 共封裝仍面臨光電耦合精度、封裝散熱、光纖對位與長期可靠度等技術挑戰。台積電、日月光憑藉著先進封裝技術整合,近年也攜手光通訊、材料與封裝廠商建立矽光子生態系,逐步串聯台灣供應鏈投入光電整合技術發展。隨著 AI 資料中心對高速互連需求持續攀升,這場從銅退光進的新革命,也正讓台灣在下一代 AI 競賽中占據更重要地位。

(首圖來源:NVIDIA)