研發階段,想要製作少量的封裝體進行後續測試,卻找不到廠商可以配合,或者一般陶瓷封裝材料亦不適合測試用的治具(socket),該如何解決?

晶片出廠的最後環節,即是進行裸晶針測(Chip Probing,簡稱 CP),在晶圓(Wafer)完成後、封裝前利用點針手法,盡可能先將壞的晶片篩檢出來,PASS 的裸晶經過封裝後,在進行最終測試(Final Test,簡稱 FT),即可完成製造並出貨。

不過,通常屬於新產品研發的晶片、或是經由客退的晶片,當須重新進行 FT,數量皆不多,業界大型封裝廠對於此類的少量晶片植入封裝體需求,排程交期都較長,甚至不接受少量客製化的封裝體晶片植入作業。

或許您會想,這還不簡單?直接使用陶瓷封裝材料植入晶片就好了呀!?

然而,陶瓷封裝材料或許可以解決部分 FT 的問題,但市面上單一規格的陶瓷封裝材料可能會遇到引腳(pin)長度及寬度,與測試治具/載具無法匹配,或是陶瓷材料(ceramic)材質與塑膠封裝體(plastic)材質不同,而影響FT結果。

您的煩惱,宜特了解本期宜特小學堂,將介紹如何使用您手邊現有的 IC 成品,進行開蓋(Decap),做成符合您需求的測試治具/載具,讓您後續能便利且有效進行 FT。

一、透過現有 IC 成品,做成測試治具/載具

首先,選擇符合您測試治具/載具的 IC 成品,接著,利用特殊開蓋方式,將部分打線及晶片露出(圖一),以利後續移除晶片及打線。

▲圖一:封裝體經過特殊開蓋方式露出晶片及部分打線

▲圖一:封裝體經過特殊開蓋方式露出晶片及部分打線

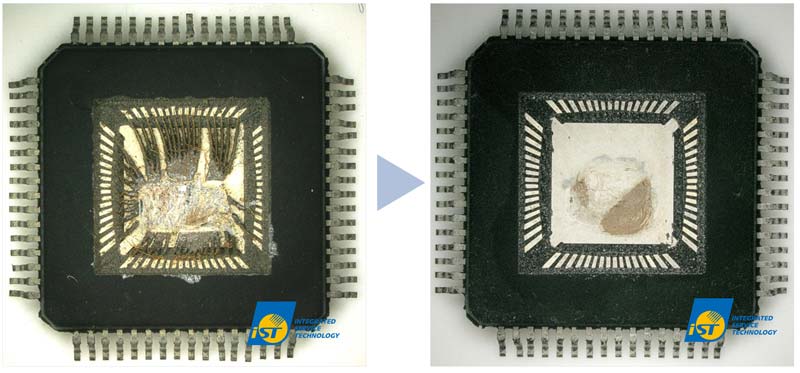

使用人工物理去除方式,將晶片及打線/引線移除(圖二),露出底板及導線架(二焊點),並保留鍍銀層。

▲圖二:宜特獨家開發 Decap 手法,去除晶片及打線(引線)

▲圖二:宜特獨家開發 Decap 手法,去除晶片及打線(引線)

最後,清除封裝體內殘餘的膠體及打線(引線),確認內部無殘留物質,為後續成為測試治具/載具進行檢查與確認(圖三)。

▲圖三:完成可以封裝打線的封裝體

▲圖三:完成可以封裝打線的封裝體

二、結合待測晶片樣品與測試治具

利用封裝黏晶,將待測晶片樣品放置於測試治具;接著,施打對應的打線/引線;最後,使用封膠將打線/引線及晶片保護隔絕,完成成品。

▲圖四:透過黏晶、引線、封膠,結合待測晶片樣品與測試治具

▲圖四:透過黏晶、引線、封膠,結合待測晶片樣品與測試治具

本文與長久以來支持宜特的您,分享經驗,若您有任何製作封裝材料需求,或是對相關知識想要更進一步了解細節,歡迎洽詢 +886-3-579-9909 分機 1066 or 1068 品牌企劃部。Email: marketing_tw@istgroup.com。

觀看更多相關文章:

(圖片來源:宜特科技)