自從 Google 發布 Gemini 3,並在多數基準測試中勝過 OpenAI 等主要競爭者後,市場對 Google 自研晶片能力的評價全面改觀。Gemini 3 完全以 Google 自家 TPU 訓練,使外界重新檢視 TPU 的性能潛力與成本效益,Meta、Anthropic 等大型客戶也開始考慮導入。不過,若 Google 想將 TPU 推向更大規模的外部市場,能否取得足夠的台積電先進封裝產能,仍是最關鍵的挑戰。

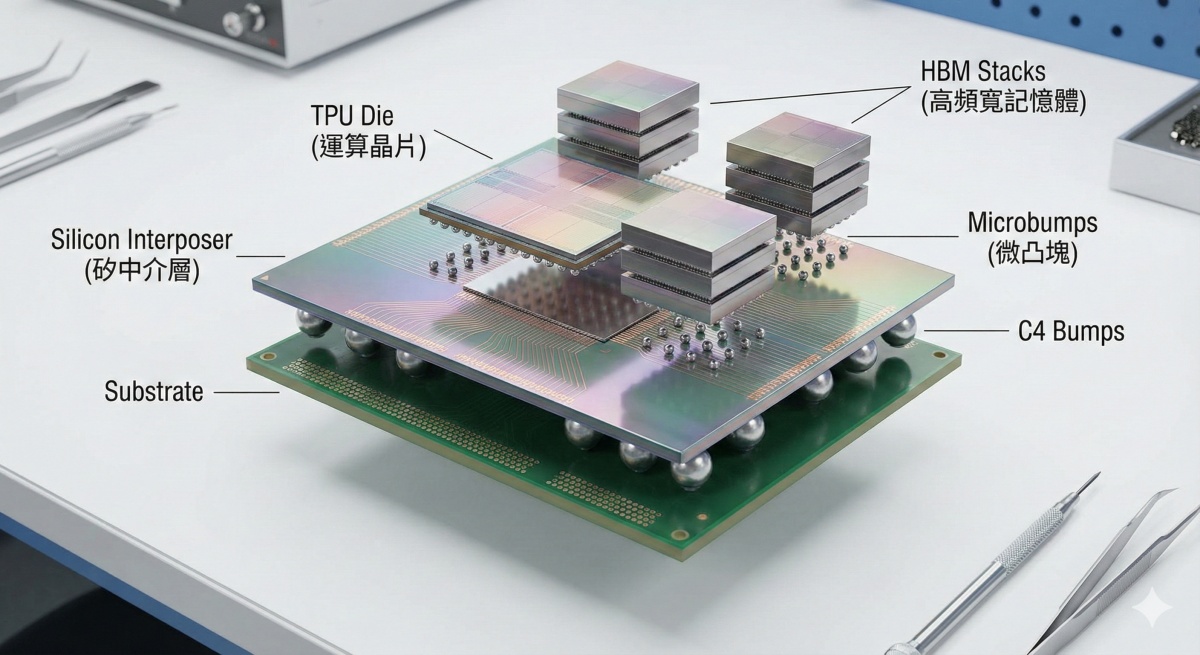

根據 Wccftech 報導,Google 最新一代 TPUv7(Ironwood)採用先進的雙晶片(dual-chiplet)設計,並採用 CoWoS 先進封裝技術(利用矽中介層),將運算核心與記憶體高密度整合於單一模組之中。

官方資料顯示,TPUv7 配備 192GB HBM 主記憶體,頻寬高達 7.4TB/s,FP8 運算能力可達 4614 TOPS,能源效率約為 4.7 TOPS/W。而要讓這些規格在實際運算環境中完全發揮,依賴的正是台積電的 CoWoS 等中介層封裝技術,才能提供足夠的頻寬密度與低延遲互連。

Google 在 TPUv7 中也將高速網路 PHY 與 routing 直接整合進內部,透過極低延遲的 D2D 互連支援大型語言模型推論,使封裝能力本身成為決定效能的關鍵。

▲ TPU CoWoS 封裝示意圖。(Source:科技新報)

然而,現階段全球先進封裝產能仍然吃緊。台積電 CoWoS 產線長期被輝達與蘋果大量占用,使得新進客戶要獲得穩定配額相對困難。市場普遍推估,Google 即便有能力滿足自家資料中心的 TPU 部署,但若想向外大規模供貨,封裝產能的排序與分配將成為最直接的限制。

近期更傳出 Google 正評估採用 Intel 的 EMIB/EMIB-T 技術,或與 Amkor 等封測業者合作,嘗試建立更分散的先進封裝供應鏈,以降低對單一供應商的依賴。

(首圖來源:Google)