根據《Tom’s Hardware》報導,SK海力士在 CES 展會上首度公開展示業界首款 16 層 HBM4 記憶體封裝,讓外界得以一窺下一代高頻寬記憶體的實體樣貌。

SK 海力士指出,此次亮相的 16 層 HBM4 記憶體堆疊採用 2,048-bit 介面,相較前一代 HBM3E,大幅提升 I/O 密度與整體頻寬配置。該公司透露,其 HBM4 記憶體堆疊運作速度可達 10 GT/s,比 JEDEC 官方規範高出約 25%。

報導指出,包括輝達在內的潛在採用者,對 HBM4 不僅著眼於效能提升,也看重其在大規模 AI 系統與超大規模資料中心應用中的效能與能源效率彈性。在高功耗、長時間運作的 AI 訓練與推論環境中,記憶體的頻寬、功耗與可靠度已成為系統設計的關鍵因素。

從封裝規格來看,HBM3/HBM3E 與 HBM4 採用相同約 10.5×12.0 mm 的封裝尺寸,但 HBM4 可支援更高的堆疊高度。以 16 層 HBM4 為例,堆疊高度約 950 微米,明顯高於 12-Hi HBM3 的約 750 微米,同時在相同面積內整合更多 I/O 與電源凸塊,進一步推升封裝複雜度。

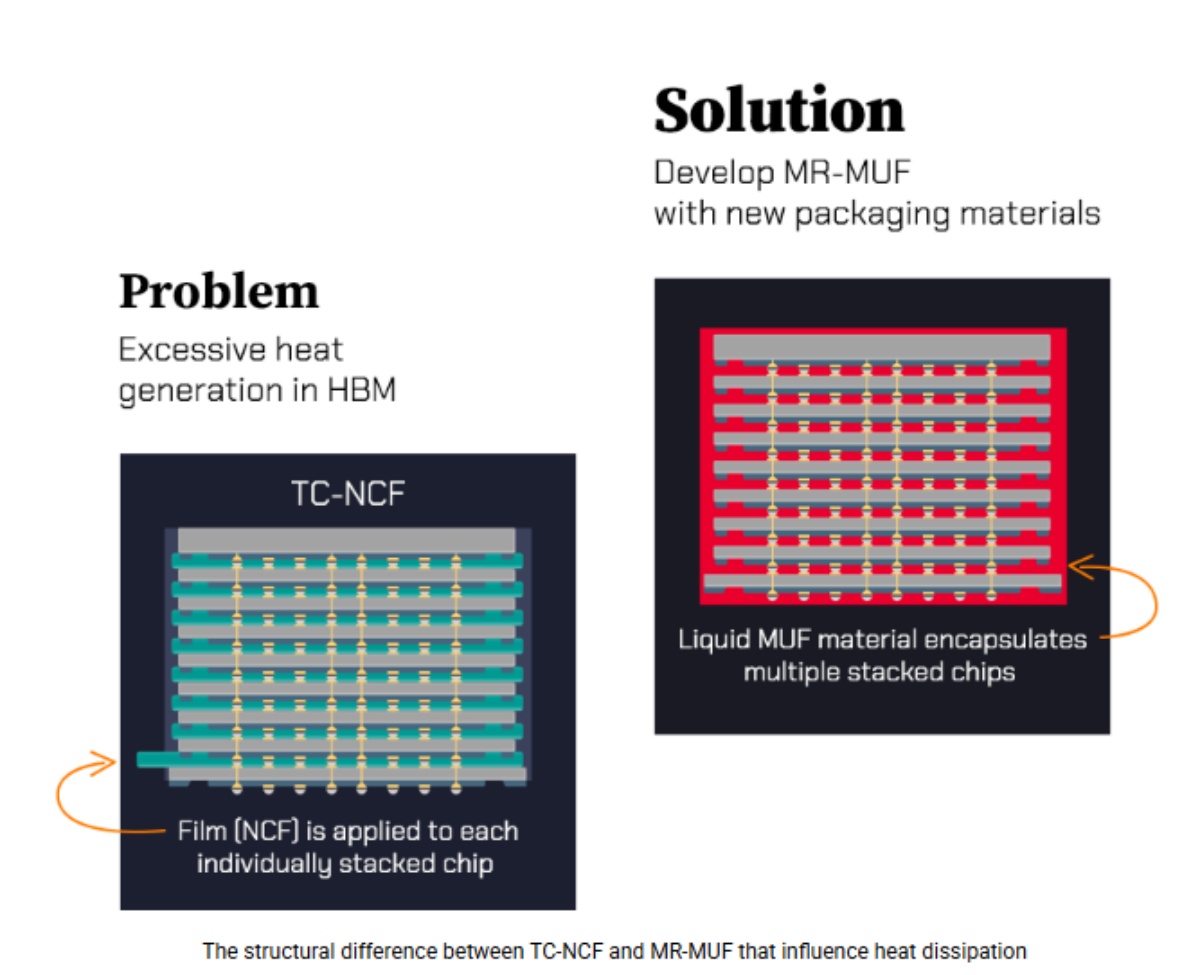

為支撐如此高密度與高堆疊設計,SK 海力士持續採用其關鍵封裝技術 MR-MUF(Mass Reflow Molded Underfill)。

什麼是 MR-MUF(Mass Reflow Molded Underfill)?

根據 SK 海力士網站,MR-MUF 結合回焊(reflow)與模封(molding)製程,在一次回焊完成多層晶片堆疊接合後,以液態環氧模封材料(EMC)填充晶片間與微凸塊間隙。

此做法不僅能強化結構穩定性,也有助於提升散熱表現、降低封裝缺陷風險,並改善整體製造良率。

(Source:SK 海力士)

(首圖來源:SK 海力士)