隨著英特爾新一代處理器 Panther Lake 進入量產準備階段,市場近期流出更多關於 Intel 18A 製程的設計細節,包括金屬層配置、GAA pitch 參數,以及背面供電(PowerVia)在不同電路區塊的實作方式。相關資訊顯示,Panther Lake 採用全 HP cell 設計,M0 金屬層最小 pitch 為 36nm,而 SRAM 並未導入 PowerVia 架構。

Forwarded Message: A Review of Intel 18A Through Panther Lake

1. Key Dimensions

Die size: ~110mm²

All cells are HP cells, including logic and SRAM (that’s right, no HD cells…)

Logic is G50H180, SRAM is 0.023, consistent with what Intel previously disclosed.

Minimum M0 is…

— Jukan (@jukan05) February 21, 2026

根據流出的設計資訊,該晶片面積約 110mm²,邏輯與 SRAM 均使用 HP(High Performance)cells,未採用 HD cells。邏輯單元標示為 G50H180,SRAM 密度為 0.023,與英特爾先前對外揭露數據相符。

M0 金屬層最小間距為 36nm;儘管 18A 規格曾提及可支援 32nm M0,但該數值對應 HD cells(H160)。在 18A 架構中,HD 與 HP 皆維持 5 tracks 設計,但 HD 為 32nm pitch,HP 則為 36nm。

在電晶體結構方面,邏輯區最小 GAA pitch 為 76nm,而 SRAM P-P line pitch 為 52nm。金屬層配置上,前側(front side)共有 15 層金屬層,背側(back side)則有 6 層金屬層,其中 BM5 層功能接近重佈線層(RDL)。

SRAM 未採 PowerVia,與結構間距有關

值得注意的是,雖然 18A 導入 PowerVia 背面供電技術,但 SRAM 區塊並未採用該架構。依英特爾先前技術說明,18A 的 PowerVia 需在 GAA 結構之間保留特定間距,以將背面電源直接連接至前側接觸層並供電至 source 端。由於 SRAM 單元 pitch 較為緊密,導入背面供電將牽動 cell 尺寸設計,因此未在本世代實作。

市場觀察指出,若在 SRAM 單元中插入 PowerVia,可能需將整體 cell 高度增加約 1.1 倍,以滿足結構間距需求。因此在 18A 世代並未全面推進。

14A 世代將調整背面供電方式

根據目前規劃,英特爾下一代 14A 製程將改採 BSCON 架構,從背面直接連接至 source 端,降低對 GAA 結構間距的限制。業界預期,在新架構下,SRAM 區塊亦可能支援背面供電。

在金屬材料方面,18A 的 MEOL contact vias 以及 BEOL V0/V1 使用鎢(W),並未採用先前市場傳聞中的鉬(Mo)。不過英特爾已規劃於 14A 世代引入 Mo。至於 M0 金屬層,目前仍採銅(Cu),且 14A 亦將延續銅材料。

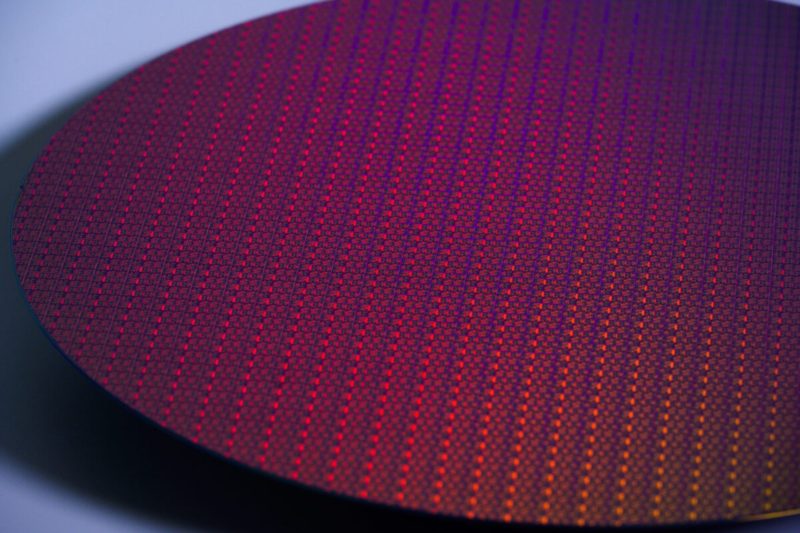

(首圖來源:英特爾提供)