受惠於半導體先進封裝市場需求強勁,半導體設備商大量科技股價走勢強勁,今(9 日)盤勢一度大漲 9.83% 至漲停,隨後在尾盤打開漲停。大量科技目前已成功建構「高階 PCB 設備」與「半導體檢測設備」雙成長引擎,並搶攻先進封裝、CPO 量測商機。

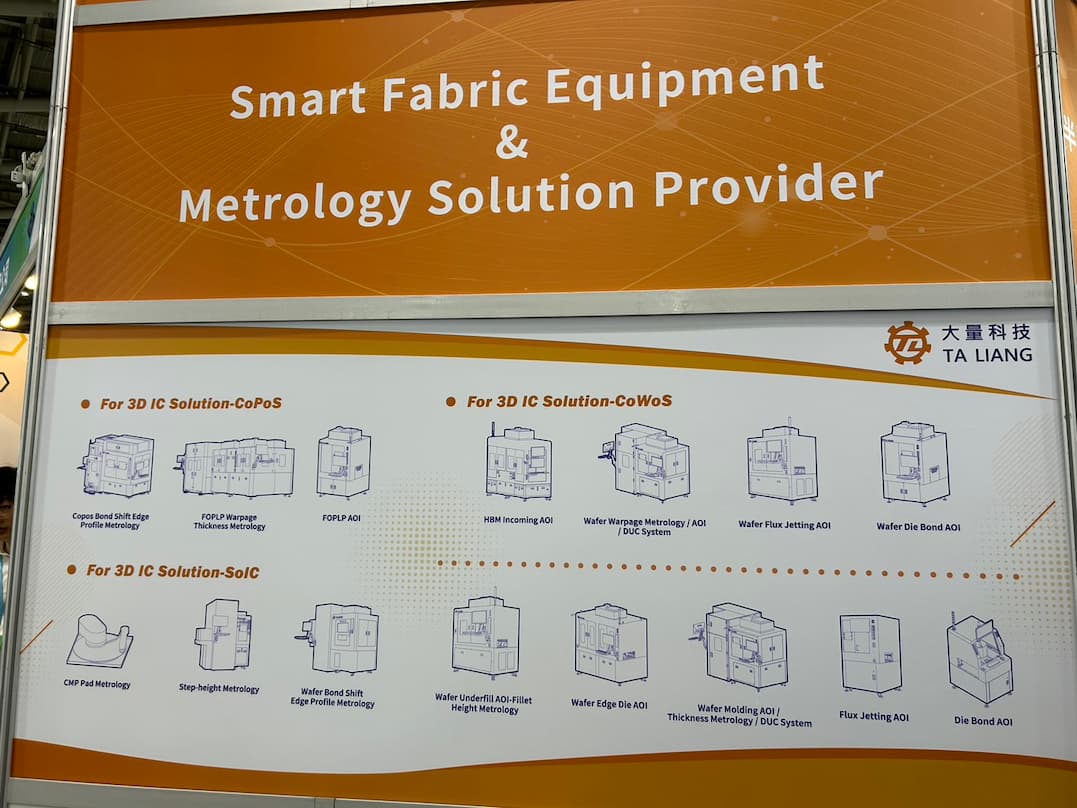

大量科技營運長李賢銘指出,團隊原先以 PCB 製程設備為基礎,近年切入半導體領域,產品重心聚焦於 AOI 檢測、量測技術與自動化(Automation)解決方案,客戶涵蓋台積電、日月光與矽品等多位指標性業者。

隨著 AI 應用帶動高階封裝需求,產業鏈出現明顯變化。先進封裝 CoWoS 可分為「CoW」(Chip on Wafer)與「oS」(on Substrate)兩部分,而大量科技在這兩個領域的市占率都非常高。目前晶片中主要有兩種類型,一種是 SOC,另一種是 HBM,而大量科技的 HBM Incoming AOI 設備是用於 HBM 來料檢測的專用設備,已經成功切入台積電供應鏈。

目前在 CoPoS 規格方面,台積電採用 310×310mm、力成為 510×510mm,日月光則為 600×600mm。大量科技會依照各客戶需求,提供專機專案化的量測與檢測服務。

針對面板尺寸是否會隨時間增大,李賢銘表示,目前觀察到更明顯是產品逐漸變厚,檢測設備會越來越重要。他解釋,產品厚度逐漸增加主要有兩個原因,第一是為了降低翹曲現象,理論上會將中介層做得稍厚,以減少內應力,使翹曲幅度降低;第二,是為了在中介層內部安置額外元件,即所謂的 Bridge,因此不得不增加整體厚度。而這些又可能會造成局部翹曲,需要進一步量測與補償。

先前傳出輝達正研發新的封裝技術 CoWoP,未來可能省去載板,現階段整體供應鏈設計與銜接封測段到量產成本都在初期階段。由於輝達主要是為了解決散熱問題,目前已經有部分實驗線進行,大量預期隨著封測廠加入,有望獲得相關商機。

李賢銘表示,CoWoS 屬於 2.5D 封裝,由一顆 SOC 晶片會與 HBM 連接,因此稱為 Die-to-Die 封裝,屬於 2.5D 類型;至於 3D 封裝,則是將原本的 SOC 進行 Die-on-Die 或 Wafer-on-Wafer 堆疊,也就是把原本單顆的晶片疊加,形成 SOIC(系統整合晶片),真正實現 3D 積體電路。

談到 CPO 部分,李賢銘認為這部分仍需處理接腳連接問題,也是大量科技的機會之一。至於何時有望落地,則和業界預期一樣約是 2027、2028 年看到進一步結果。

(首圖來源:科技新報)