根據 Wccftech 報導,繼 AMD 在 CES 2026 發表採用台積電 2 奈米製程的 EPYC Venice 處理器後,近日網路上流出最新爆料,揭露了更多官方尚未公開的架構細節。

AMD 在 Venice 世代將核心數推升至新高,其中搭載 Zen 6C 架構的版本最高可達 256 核。在設計上,AMD 透過更高密度的計算晶粒(CCD)與全新的雙 IO Die 架構,試圖同時因應高核心數與 AI 伺服器對 I/O 頻寬快速升溫的需求。

Venice IOD: ~375mm² N6 x 2

Turin IOD: ~426mm² N6 x 1Zen6c CCD: 32 Cores = ~155mm² N2

Zen5c CCD: 16 Cores = ~85mm² N3E https://t.co/n4GJGNWqlo— Hassan Mujtaba (@hms1193) January 12, 2026

爆料資訊指出,EPYC Venice 的高密度版本核心在於新一代 Zen 6C 計算晶粒。每顆 Zen 6C CCD 可容納 32 顆核心,較前一代 Zen 5C 的 16 核設計直接翻倍,使 AMD 能在僅使用 8 顆 CCD 的情況下,達成更高的 256 核心配置。

快取配置同樣是升級重點。每顆 Zen 6C CCD 內建 128MB L3 快取,使整顆處理器的 L3 快取總容量高達 1GB。在多核心伺服器負載中,這有助於降低對主記憶體的依賴與延遲。

在製程策略上,負責運算的 CCD 採用台積電 2 奈米(N2P)製程,以追求極致效能;而負責 I/O 的 IO Die 則維持 6 奈米製程。

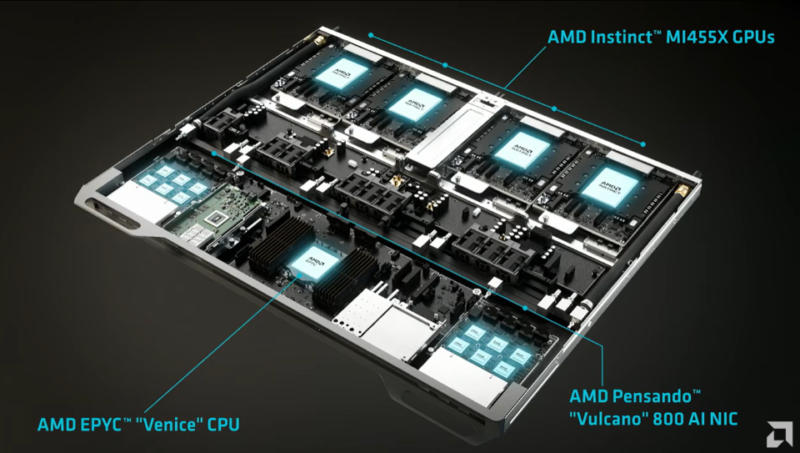

值得注意的是,EPYC Venice 改採雙 IO Die 架構,兩顆 IO Die 總面積達 750mm²,遠超前代的單一 IO Die 設計。這意味著記憶體通道、PCIe 與 CXL 擴充能力將大幅提升,更有利於支援 AI 伺服器中 GPU 與高速網路設備的密集部署。

(首圖來源:影片截圖)