韓國科學技術院(KAIST)近期發表一篇長達 371 頁的論文,詳細描繪高頻寬記憶體(HBM)技術至 2038 年的演進路線,涵蓋頻寬、容量、I/O 寬度與熱功耗等面向的成長。該藍圖涵蓋從 HBM4 到 HBM8 的技術發展,包括先進封裝、3D 堆疊、嵌入式 NAND 儲存的記憶體中心架構,以及以機器學習為基礎的功耗控制手法。

根據該藍圖,HBM 單堆疊容量將從 HBM4 的 288GB 增加至 384GB,HBM7 容量增加至 5,120GB 至 6,144GB;每個堆疊的功耗也提升,從 HBM4 的 75W 增至 HBM8 的 180W。

在 2026 年至 2038 年間,HBM 的頻寬預期將從 2 TB/s 成長至 64 TB/s,數據傳輸速率則從 8 GT/s 提升至 32 GT/s;I/O 數從 HBM3E 的 1,024,增加到 HBM4 的 2,048,最終在 HBM8 高達 16,384。

報導稱,目前 HBM4 技術已大致明朗,而 HBM4E 則透過客製化的基礎晶片(base die)設計,針對 AI、高效能運算(HPC)、網通等應用提供更大彈性。

預期 2029 年推出的 HBM5,將延續 HBM4 的數據傳輸速率,I/O 數則翻倍至 4,096、頻寬升至 4 TB/s,單堆疊容量預期升至 80 GB、功耗達 100W,並需要更先進的散熱技術。

目前業界已在 HBM4 研究無焊接直接鍵合(direct bonding),KAIST 預期 HBM5 將繼續採用 MR-MUF 技術。此外,HBM5 將整合 L3 快取、LPDDR、CXL 介面與熱感應監控功能,並開始導入 AI 工具以最佳化實體布局。

至於 HBM6 預期將於 2032 年接棒,傳輸速度將達 16 GT/s、頻寬達 8 TB/s,單堆疊容量高達 120 GB、功耗為 120W。HBM6 將採用無凸塊直接鍵合技術,並結合矽與玻璃的混合型中介層(hybrid interposer)設計。在架構部分,則導入多塔式(multi-tower)記憶體堆疊、內部網路交換機設計,以及大量矽穿孔(TSV)分布。AI 設計工具的應用範圍也將擴大,導入生成式設計來進行訊號與電源建模。

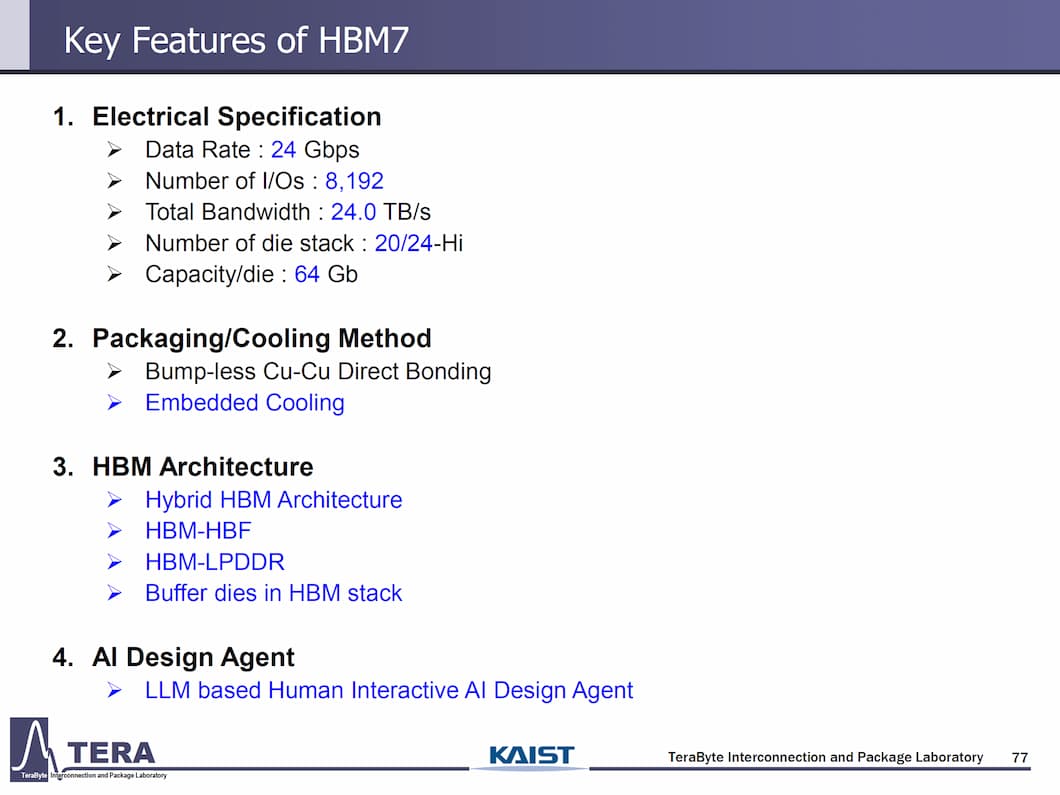

到了 HBM7 和 HBM8,將進一步突破現有概念,兩種都將採用無凸塊直接鍵合技術,以及內嵌式冷卻解決方案。其中,HBM7 也將引進全新的 HBM-HBF 和 HBM-3D LPDDR 架構。此外,採用 HBM7 的解決方案預期將走向超大型與多晶片組(multi-chiplet)設計。

HBM8 傳輸速率將達 32 GT/s,單堆疊頻寬高達 64 TB/s,容量預計可擴充至 240 GB。封裝技術則進化為全 3D 堆疊並採用雙面中介層(double-sided interposer)與內嵌式液冷通道。

其中,HBF(High-Bandwidth Flash) 架構主要為了解決記憶體密集型大型語言模型(LLM)推論所需的龐大容量需求。在 HBF 架構中,與傳統使用 DRAM 不同,製造商會採用多達 128 層的 NAND 快閃記憶體,建構出 16 層堆疊,並透過專屬的 HBF TSV 技術進行連接。

也因此,每一個 HBF 堆疊會與一個 HBM 堆疊並聯,可額外提供高達 1TB 容量,並透過 2 TB/s 的 HBM 與 HBF 之間的高速互連進行資料交換。這些模組再透過主機板上的記憶體網路交換器(memory network switch),以 128 GB/s 的雙向互連速率連接至其他元件。

雖然 HBM7 與 HBM8 名義上仍屬於 HBM 家族,但架構預期將與現今所知的 HBM 不同。據悉,HBM5 引入 L3 快取與 LPDDR 介面,而 HBM7/8 則預期將導入 NAND 介面,使資料直接從儲存裝置移動至 HBM,僅需最少的CPU、GPU 或 ASIC 介入。

如此一來,每個堆疊功耗達 180W,而 KAIST 預期 AI 代理系統將管理散熱、電源與訊號路徑的最佳解。除了剛剛上述的 GPU、HBM、HBF 堆疊外,KAIST 也展示 GPU、HBM、HBM 堆疊,及 GPU、HBM、LPDDR 堆疊的示意圖。

- Next-Gen HBM Architecture Detailed Including HBM4, HBM5, HBM6, HBM7 & HBM8: Up To 64 TB/s Bandwidth, 240 GB Capacity Per 24-Hi Stack, Embedded Cooling

- HBM development roadmap revealed: HBM8 with a 16,384-bit interface and embedded NAND in 2038

(首圖來源:shutterstock)