隨著台積電 2 奈米預期年底量產,明年(2026 年)下半年正式跨入埃米時代,晶片微縮已達到物理極限,原子層沉積(Atomic Layer Deposition,簡稱 ALD)成為延續摩爾定律、半導體微縮的關鍵技術之一。對此,《科技新報》特地專訪荷蘭半導體製造設備大廠 ASM 技術副總裁 Glen Wilk,幫助讀者更了解 ALD 在製程微縮的重要性。

ALD 為何那麼重要?跟 CVD、PVD 差異在哪?

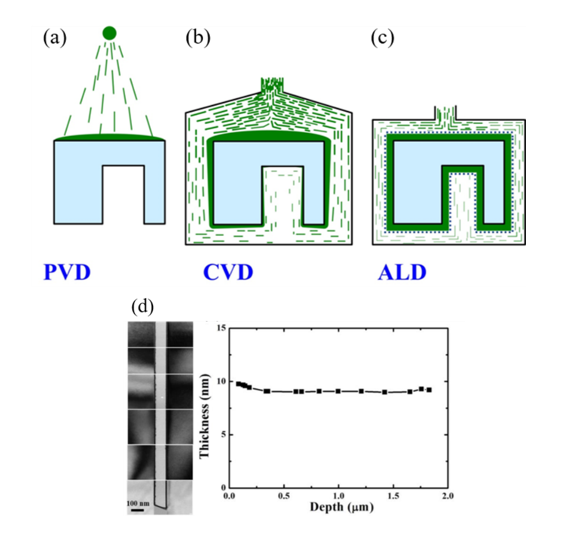

ALD 主要特性之一是逐層沉積原子,是可以將材料一層一層成長的薄膜製程技術,「你可以想像成下雪,每當只落下一層雪花時,可使沉積非常均勻且擁有良好的覆蓋性」,Wilk 表示,ALD 技術能使沉積沿著邊緣沉積,甚至在底部、側面或上方都能逐層沉積。

相比之下,PVD(物理氣相沉積)則是「直線沉積」,如同箭一樣只能沿著射向(直線路徑)飛,因此無法轉彎或在底部、角落沉積,因此 PVD 的覆蓋能力非常有限,只能往一個方向沉積。

至於 CVD(化學氣相沉積)與 ALD 較為相似,但每次沉積不是單層原子,而是多層原子,雖然具有一定的覆蓋能力、可沉積到凹角,但不如 ALD 精準。Wilk 指出,尤其是特地部分(如底部、角落)進行精確控制時,CVD 就做不到,雖然速度較快,但精準度不如 ALD。

▲ PVD、CVD、ALD 三種沉積方式示意圖。(Source:國家實驗研究院)

當製程走向 2 奈米以下,ALD 技術面臨三大挑戰

隨著 GAA、3D 架構發展,由於深寬比更高、溝槽更深窄,對於沉積覆蓋性、精準度與厚度控制要求更高。Wilk 表示,有些結構會有兩片不同片層,需要頂部和底部都進行沉積,當兩邊可能在中間相遇時,要避免發生「堵塞」(clogging)狀況。以吸管為例,若在吸管內側塗色,很容易卡在前方或入口處,加上內部又細又窄,材料可能堆積上方,難以深入底部,因此塗得均勻且厚薄度控制得當,變得更困難。

第二個挑戰是「區域選擇性沉積」(Area Selective Deposition,簡稱 ASD)。傳統進行 ALD 技術時,會精確且覆蓋所有地方,但現在需求轉向在晶片特定區域沉積,因此「選擇性沉積」和「局部沉積」成為重要技術,能節省後續曝光和加工步驟,從而降低成本。

第三個挑戰是「填縫」(Gap Fill)。若在結構之間填充時,傳統方式會讓兩側材料在中間相遇並形成一條縫隙(Seam),當後續再經歷蝕刻或其他製程,縫隙恐越撐越大,最終導致裂開。解決辦法是透過「無縫隙填充」(Seam-free gap fill)的方式,直接完整填滿中間結構,避免兩側材料碰在一起產生縫隙。

▲ CFET 為圖右的架構,三星稱為 MBCFET。(Source:三星)

這些都是製程微縮下遇到的挑戰,Wilk 表示,ASM 已率先開發選擇性沉積(ASD)技術,幫助客戶有效解決先進製程挑戰,提升製程良率、元件可靠性與整體效能。

他也指出,若進一步走到 CFET 架構,ALD 沉積將面臨更多挑戰,主要在「低溫沉積」和「選擇性沉積」,要求將比 GAA 更嚴格。GAA 挑戰是一層堆疊,而 CFET 是在這上面再堆疊一層(即堆疊兩層以上),如同蓋高樓一樣,如何從上到下實現超薄且均勻的沉積,且不能產生縫隙,是個棘手問題。

此外,CFET 對「低溫沉積」要求更高。過去 GAAFET 架構是一次同時完成製程,所以對高溫處理沒問題;但到 CFET 架構,可能面臨需先製造上面兩層、再進行下面兩層,而製作新結構時需要高溫,使得已完成的舊結構需面臨二次高溫,恐導致損壞或性能退化。此外,低溫沉積又會面臨元素(如碳)殘留問題,亦是挑戰之一。

▲ 從上圖可知,CFET 架構的溝槽更得深窄,沉積也變得棘手。(Source:台積電)

化學材料+硬體雙引擎!ASM 靠研發團隊維持 ALD 技術領先

針對這些挑戰,ASM 決定從材料和硬體設備下手找尋新解方。該公司旗下的企業研發部(Corporate R&D,簡稱 CRD)負責開發先進化學與製程解決方案。一部分團隊位於芬蘭,與赫爾辛基大學合作,主要著重在材料開發、前驅物篩選以及新路徑探索;另一團隊與半導體研發中心 imec 合作,進一步驗證和模擬真實環境測試。

這些團隊專注於研究新的化學反應與新分子,以克服目前特定區域沉積、堵塞問題。Wilk 強調,這需要大量全新的化學配方與創新,這也是 ASM 獨有的優勢。此外,做為 ALD 領先設備供應商,ASM 也在改善硬體設計,使其與新化學配方、新分子與新解決方案相匹配,並有效輸送化學物質,使其能在晶圓上達到均勻覆蓋,同時保持高效率與高速度。

「ASM 早在 1999 年收購芬蘭公司 Microchemistry,而 ALD 技術正是由這間公司發明,ASM 也傳承了這項專業能力。」Wilk 認為,化學專業是 ASM 優勢之一,能根據這些化學特性去設計對應的硬體設備是另一大優勢,「透過化學與硬體的結合,正是我們一直保持領先、並視為核心差異化的關鍵所在」。

全面布局新材料研發,ASM 瞄準無縫隙填充、低溫沉積與選擇性沉積

ASM 研究重點包括各類型填隙材料(二氧化矽、氮化矽)、新型閘極堆疊材料(功函數金屬與偶極)、高導熱絕緣層、新型接觸材料、低溫磊晶、矽/矽鍺 3D DRAM 磊晶堆疊等,也針對各種薄膜進行研究,解決客戶在上述製程中遇到的問題。

此外,ASM 旗下也有負責規劃先進技術的前瞻部門,與客戶密切合作,探索潛在解決方案。目前公司正著手開發新材料,例如能快速導熱、有效散熱的材料,以及開發在極薄條件下依然運作良好(如良好絕緣或導電)的新材料,以取代傳統較厚的膜層,另在化學前驅物也有諸多合作。

透過 CRD 早期合作,ASM 能及早了解客戶需求並測試解決方案,可在真實環境中不斷「測試與學習」,提高成功率,提前向客戶推廣開發的新材料層,這是 ASM 獨有的橫向/企業級的研發,也是公司的差異化優勢。

Wilk 表示,不管是「無縫隙填充」、「低溫沉積」或者「選擇性沉積」,都是目前競爭最激烈的領域。ASM 已持續進行化學材料的開發,搭配專門與之相匹配的硬體設計,且可簡化製程步驟、大幅提升產能,進一步為客戶節省成本。

除了 ALD 外,磊晶也成為 GAA 時代下一大難題

在摩爾定律持續推進製程微縮,FinFET 時代電晶體通道的厚度主要由微影與蝕刻決定;隨著技術演進至 GAA 架構,矽通道則改由具備原子級精準度的磊晶製程直接生長而成。

Wilk 表示,當來到 GAA 時代,磊晶會面臨「低溫」與「生長奈米片(Nanosheet)」兩大挑戰,前者因背面供電技術,使溫度控制更困難,加上低溫環境容易引入雜質,導致品質下滑,成關鍵挑戰之一;後者在建構通道製程時,必須交替生長磊晶,製作出間距分開的多個矽通道,這又涉及到界面銳利度(Interface Sharpness)問題。

對此,ASM 也將技術延伸至磊晶領域,強調公司磊晶設備的硬體設計與競爭對手不同,能在低溫下實現更好控制,同時沉積出非常均勻且高品質的薄膜。在先進封裝的「混合鍵合」(Hybrid Bonding)部分,ASM 可提供混合鍵合層及相關表面處理技術,另在晶粒堆疊整合過程中,須透過高導熱性的絕緣層來散熱,也成為 ASM 另一大機會。

「台灣團隊對 ASM 來說非常重要!」ASM 指出,台灣做為全球半導體產業的核心樞紐,一直都是公司業務發展策略中最不可或缺的一部分,去年啟用新竹辦公室將聚焦研發與客戶支援,而台南也設有培訓中心,負責支援本地需求及培育其他國家工程師的培訓中心;至於全球布局部分,ASM 目前主要製造基地位於新加坡、第二製造中心位於韓國,現有產能相當充足。為了因應目前政經狀況,ASM 也將於 2027 年在美國新增研發單位據點,做為新工具測試地點。

(首圖來源:科技新報)