根據日經報導,大日本印刷(DNP)宣布開發出可支援 1.4 奈米邏輯製程的奈米壓印(Nanoimprint Lithography, NIL)模板技術,能大幅降低先進半導體製造的電力消耗,預計可將相關曝光流程所需能耗壓至傳統方式的約十分之一,並計劃自 2027 年起量產,並供佳能(Canon)NIL 設備應用。

在先進製程持續微縮下,EUV 雖是現階段最成熟的微影方案,但設備投資動輒數億美元、耗電量高,使晶片製造成本不斷上升。

佳能因此布局奈米壓印,以「直接壓印電路」的方式作為對沖 EUV。然而 NIL 難以突破 2 奈米以下節點。此次 DNP 高解析度模板的推出,使 NIL 首度跨入 1.4 奈米級距。

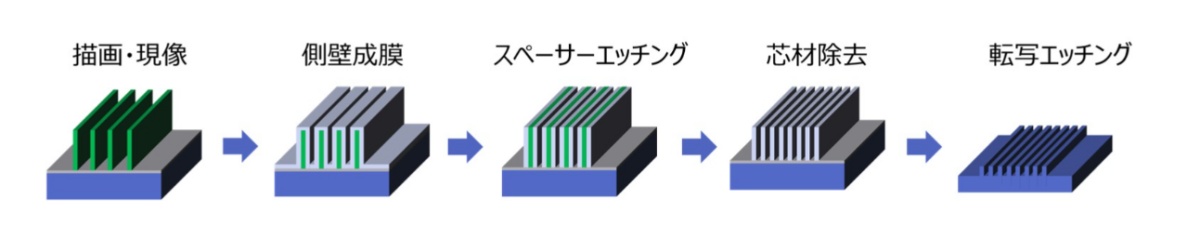

技術上,DNP 運用自對準雙重圖樣化(Self-Aligned Double Patterning, SADP)提升圖形密度,讓模板解析度得以進一步微縮;再結合多年累積的光罩與晶圓製程技術,使 NIL 模板能穩定達到 10 奈米線寬,對應 1.4 奈米邏輯製程所需精度。

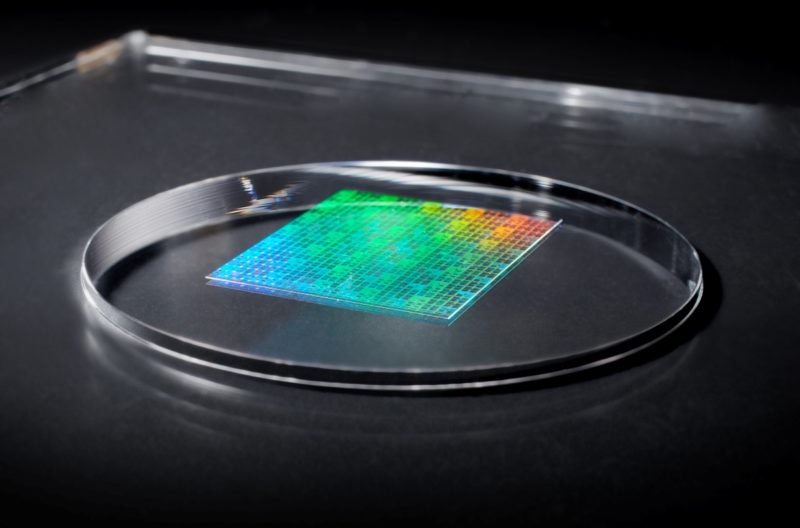

(Source:DNP)

除了能應用於 NAND 型快閃記憶體,也能滿足智慧型手機、資料中心等領域對最先端邏輯半導體微縮化的需求。

儘管如此,業界普遍認為 NIL 與量產仍有顯著距離,最大瓶頸集中在光罩壽命與缺陷控制。奈米壓印的模板上具有微米級甚至奈米級結構,極為脆弱,每次壓印都會造成磨耗,使模板壽命有限;同時,一旦模板或晶圓表面存在微小雜質,便可能直接形成缺陷並大幅拉低良率。因此還是很難超越 ASML 的 EUV。

台積電與三星均對奈米壓印技術表示高度興趣,並將其視為 2 奈米以下先進製程的潛在選項。然而兩家公司現有廠房皆依照 EUV 與傳統光罩架構設計,使導入 NIL 面臨困難。佳能已在 2024 年向美國德州電子研究院(Texas Institute for Electronics)出貨首台奈米壓印設備,市場正在觀察其可用性。

- New Japan tech said to slash power use in making next-gen 1.4-nm chips

- 最先端半導体向けに回路線幅10nmのナノインプリント用テンプレートを開発

(首圖來源:DNP)