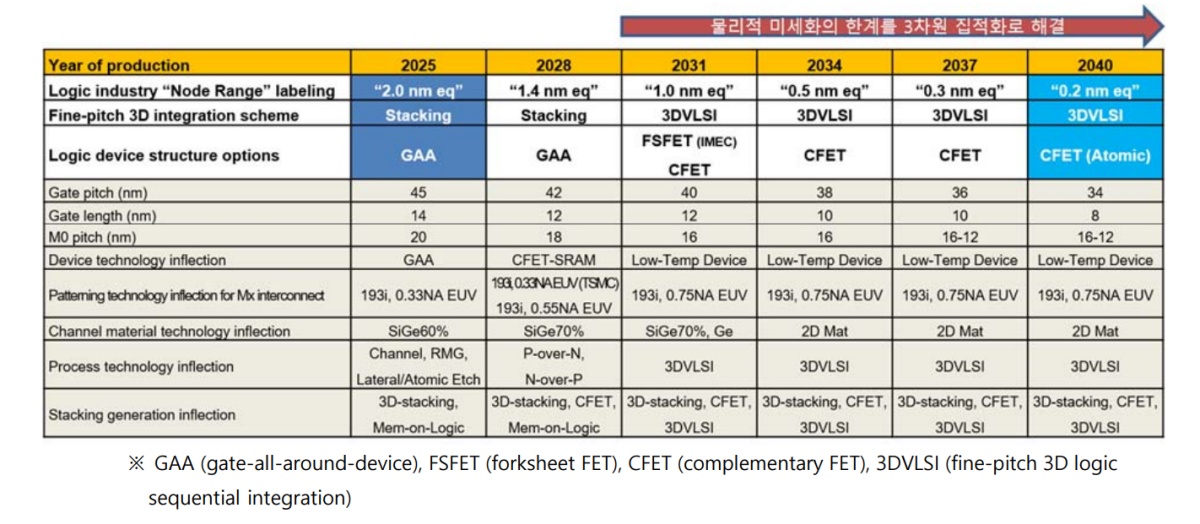

根據韓國半導體工程師協會發表的《반도체 기술 로드맵 2026》(半導體技術路線圖 2026),全球半導體產業正規劃在未來 15 年內,將先進邏輯製程從現行的 2 奈米節點,逐步推進至 2040 年的 0.2 奈米,正式進入埃米(Å)世代。隨著傳統線寬微縮逐漸逼近物理極限,未來製程演進將不再僅仰賴微影技術,而是轉向結構、材料與系統層級的全面革新。

2040 後將迎來埃米世代,EUV 可能迎來瓶頸

從時間軸來看,路線圖預期 2025 年左右進入 2 奈米世代,並於 2031 年前後推進至 1 奈米級;到了 2040 年,邏輯電路線寬將進一步縮小至 0.2 奈米。儘管 0.75NA EUV 可在 2030 年前後帶來更細線寬,但基於微影的物理微縮將逐步趨於飽和,製程競爭的重心勢必轉向晶片架構與整體系統設計。

(Source:ISE,同下)

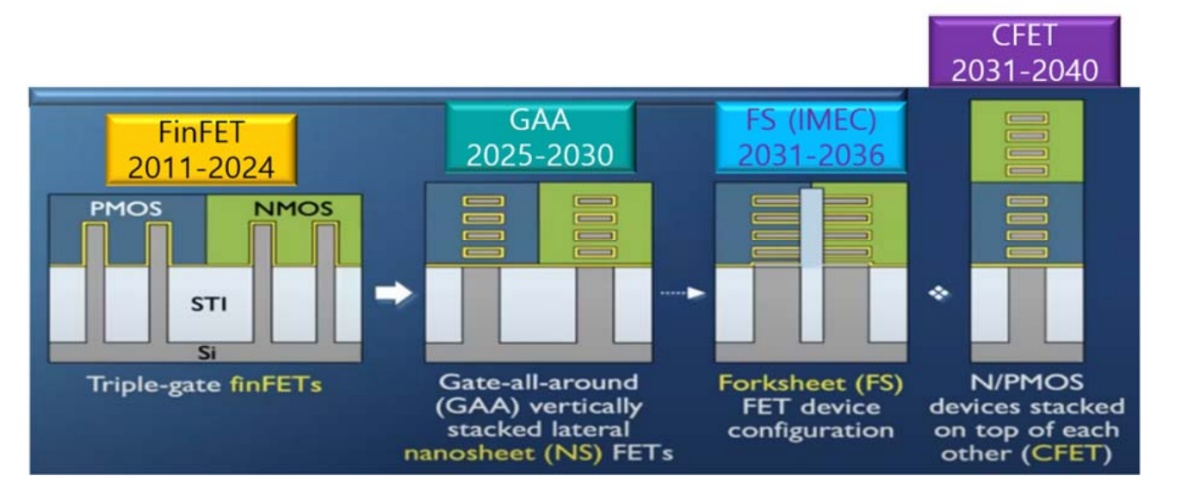

電晶體與製程朝向立體化

為延續摩爾定律,邏輯元件將由 FinFET 轉向 GAA(Gate-All-Around),並進一步演進至 CFET(Complementary FET) 等三維電晶體結構,透過將 PMOS 與 NMOS 垂直堆疊,突破平面密度限制。配合 Monolithic 3D(單晶 3D) 製程,以及由 DTCO 邁向 STCO(系統-製程共同最佳化) 的設計思維,未來效能提升將來自整體架構重整,而非單一製程節點的微縮。

記憶體同步進化,異質整合與高層數 DRAM 成關鍵

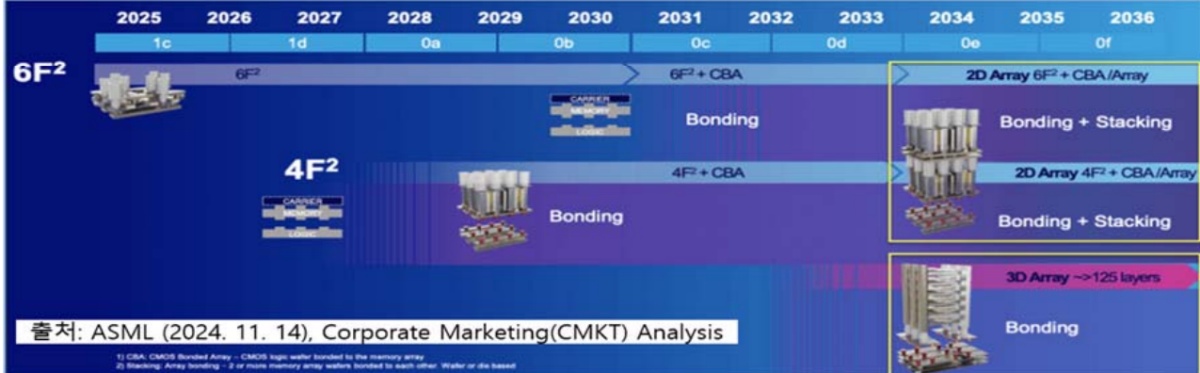

除了邏輯製程,記憶體技術的演進節奏與 0.2 奈米邏輯製程高度同步。在 DRAM 領域,傳統 BCAT 架構預期將在 7~8 奈米遭遇微縮極限,未來將轉向垂直通道電晶體、堆疊式 DRAM、4F² 單元,以及透過 Hybrid Bonding 將 CMOS 電路直接與記憶體陣列結合的 CBA(CMOS Bonded Array) 架構,延續密度與效能提升。

在 AI 應用推動下,高頻寬記憶體(HBM) 的重要性進一步放大。路線圖指出,HBM 將透過更高層數堆疊、混合鍵合與散熱設計,HBM 預測 2031 年將有 20 層、8 TB/s,並在 2040 年達到 30 層以上、128 TB/s 的頻寬水準。。

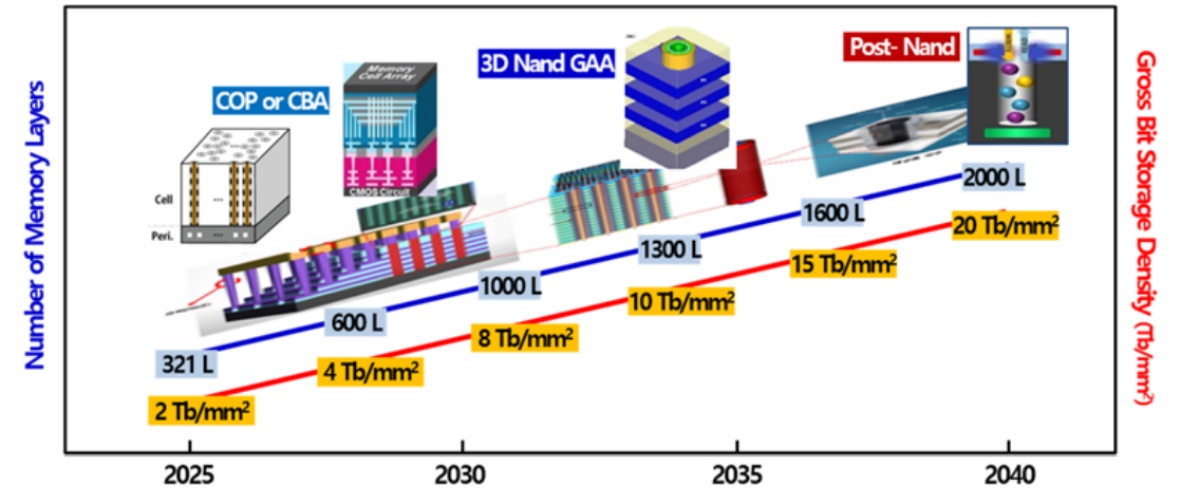

至於 NAND Flash,則走向「以層數換密度」的發展路徑,預期自 321 層,推進至 2031 年約 1,000 層,並在 2040 年挑戰 2,000 層。

進入超越摩爾定律時代(More than Moore)

半導體產業正藉由邏輯與記憶體的 3D 化、Hybrid Bonding 及系統級架構重整,提升單位面積整合密度並降低互連延遲,以在不依賴線寬微縮的情況下,滿足未來 AI 或其他產業對於高速、低功耗的需求。

(首圖來源:AI 生成)