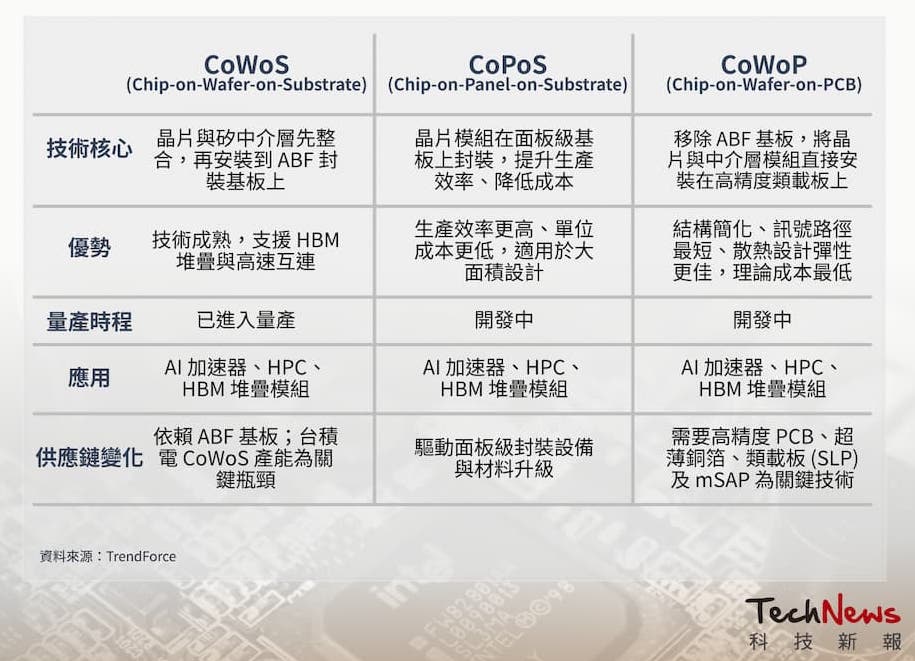

隨著摩爾定律逐漸逼近物理極限,晶片製程微縮效益有限,業界正尋求新的破口,而先進封裝(Advanced Packaging)成為近年最受矚目的技術之一。隨著台積電的 CoWoS 產能逐漸供不應求,陸續出現 CoPos、CoWoP 等新技術,但這兩個技術和 CoWoS 差在哪裡?何時開始導入?《科技新報》整理相關資訊帶你一次看。

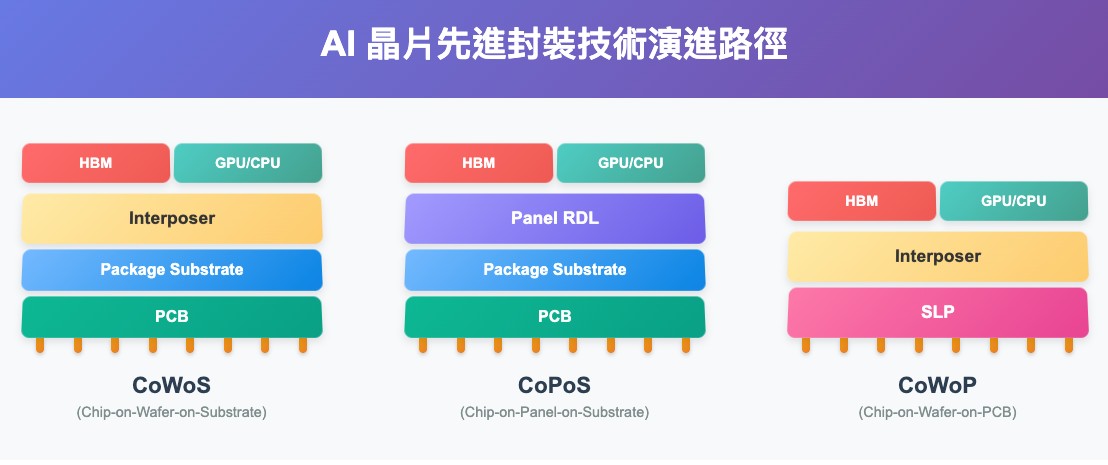

從下圖可以看到,其實 CoWoS、CoPos、CoWoP 堆疊方式有些不同,例如 CoPoS 主要是將中介層改成面板 RDL;CoWop 則是透過開發技術含量較高的 PCB 主機板,來取代 IC 載板。

接著,我們來仔細介紹這三項技術的主要差異,但在此之前,要先了解這些延伸技術的根源──台積電的先進封裝 CoWoS。

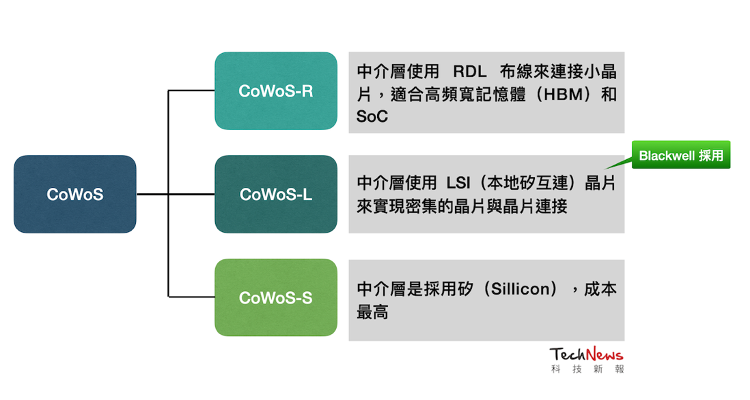

台積電先進封裝技術 CoWoS,還細分為 CoWoS-S、CoWoS-R、CoWoS-L

CoWoS 是台積電的 2.5D、3D 封裝技術,可分成「CoW」和「WoS」來看。

CoW(Chip-on-Wafer)是晶片堆疊,WoS(Wafer-on-Substrate)則是將晶片堆疊在基板上,所以 CoWoS(Chip-on-Wafer-on-Substrate)的意思是把晶片堆疊起來,再封裝於基板上,最終形成 2.5D、3D 的型態,可減少晶片的空間,同時減少功耗和成本。

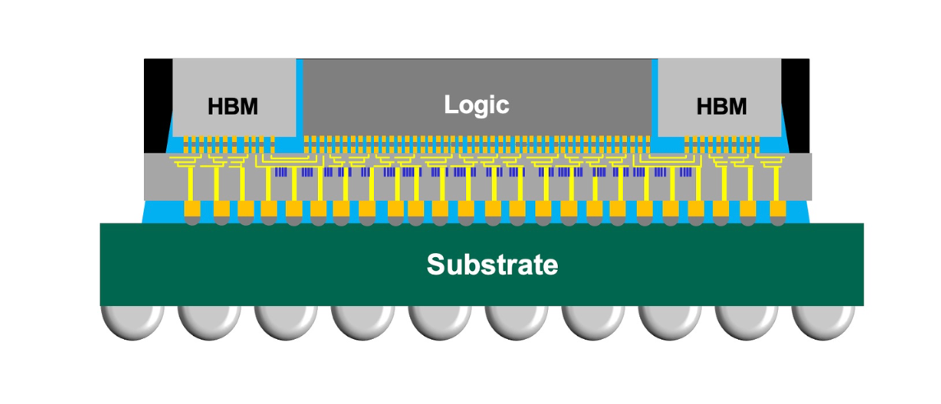

CoWoS 是先將邏輯晶片與 HBM(高頻寬記憶體)安裝在矽中介層(Interposer)上,透過中介層內部微小金屬線來整合左右不同晶片的電子訊號,同時經由矽穿孔(TSV)來連接下方基板,將訊號導向下方,最終透過金屬球(bumps)與外部電路銜接。

其中,CoWoS 技術又分成 CoWoS-R、CoWoS-L 和 CoWoS-S 三種技術,因中介層材質不同,成本也不同,客戶可依據自身條件選擇要哪樣技術。

目前成本最高的是 CoWoS-S,因為其中介層採用「矽」(Sillicon),也是主流方案,如 NVIDIA H100、AMD MI300 都使用 CoWoS-S。然而,CoWoS-S 因使用高純度矽材與 TSV 製程,加工難度大,且中介層面積受曝光機台限制,封裝尺寸上限大約為 2,500 平方毫米。

▲ CoWoS-S。(Source:台積電,下同)

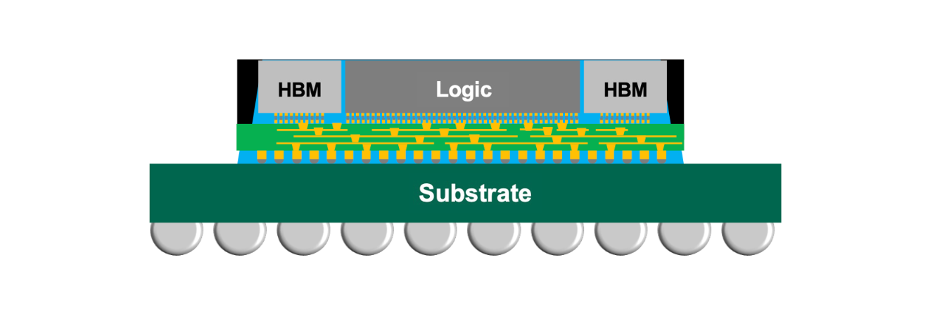

CoWoS-R 採用 InFO 中用到的互連技術,其中介層使用 RDL(重布線層)來連接小晶片之間,支援彈性封裝設計,適合對成本較為敏感的 AI ASIC 應用、網通設備或邊緣AI。

▲ CoWoS-R。

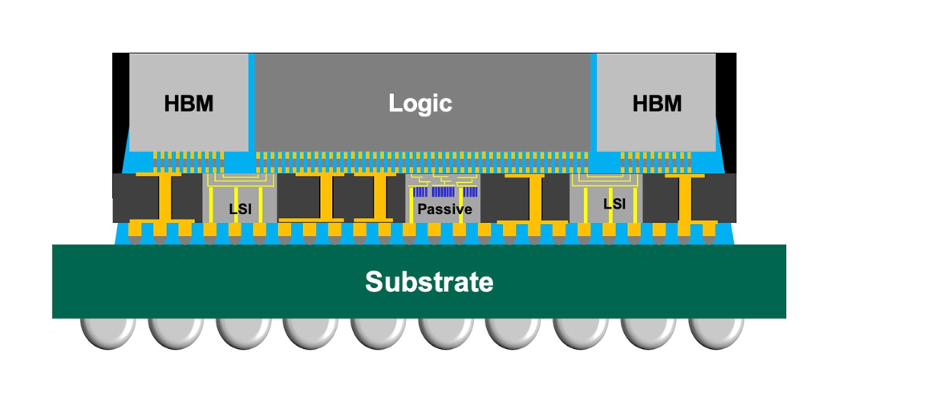

至於 CoWoS-L 成本介於 CoWoS-S、CoWoS-R 之間,中介層使用 LSI(局部矽互連,Local Silicon Interconnect)和 RDL,即局部區域以矽中介層串連晶片,其他區域用 RDL 或基板,實現密集的晶片與晶片連接,支援高達 12 顆 HBM 記憶體的堆疊應用,可說結合 CoWoS-S 和 CoWoS-R/ InFO 的技術優點。

▲ CoWoS-L。

台積電高效能封裝整合處處長侯上勇在 Semicon Taiwan 2024 專題演講中提到,由於頂部晶片(Top Die)成本非常高,CoWoS-L 是比 CoWoS-R、CoWoS-S 更能滿足所有條件的最佳解,因此會從 CoWoS-S 逐步轉移至 CoWoS-L,並稱 CoWoS-L 是未來藍圖要角。

有趣的是,也有人認為 CoWoS-L 意思是「Large」,專為超大型 AI 訓練平台與高整合度應用而設計,延續 CoWoS-S 架構,但進一步突破矽中介層尺寸限制,開發可支援超過 2,500 平方毫米的超大面積中介層技術。

▲ CoWoS 技術路線圖。(Source:科技新報整理)

CoWoS「面板化」!解決成本、大尺寸晶片翹曲問題

了解 CoWoS 的技術分支後,接著來聊聊 CoPoS 和 CoWoP。

由於 AI 晶片越來越大、設計越來越複雜,傳統的圓形晶圓在面積利用率和封裝效率逐漸受限,因此開始走向「以方代圓」,以面板(Panel)取代晶圓(Wafer),將晶片排列在矩形基板上,最後再透過封裝製程連接到底層的載板上,讓多顆晶片可以封裝一起,也就是所謂的「CoPoS」(Chip-on-Panel-on-Substrate)。

▲ CoPoS 示意圖。(Source:亞智科技)

CoPoS 是將晶片排列在方形「面板 RDL 層」,取代原先圓形的矽中介層,強化不同導電層與材料間的電路互連布局,提升面積利用率與產能。此外,因導入玻璃或藍寶石等新材料,方形尺寸可進行多顆晶片封裝、整合不同尺寸晶片,同時支援更大光罩、緩解晶片越大越明顯的翹曲問題。

業界分析,CoPoS 是 CoWoS-L 或 CoWoS-R 的「矩形」變形概念,將傳統 300 毫米矽晶圓改為方形面板設計,尺寸 310×310 毫米、515×510 毫米或 750×620 毫米等,目前供應鏈研發方向皆以台積電釋出的規格為主。不過 CoPoS 初步尺寸選定採用 310×310 毫米。

業界傳出,台積電預計 2026 年設立首條 CoPoS 實驗線,目標 2028 年底至 2029年之間實現量產,第一個客戶就是 NVIDIA。此外,未來 CoPoS 封裝的方向,主要鎖定 AI 等高階應用,採用 CoWoS-R 製程的將鎖定博通,CoWoS-L 則目標服務 NVIDIA 及 AMD。

至於 CoPoS 與 FOPLP(扇出型面板級封裝,Fan-out Panel Level Packaging)差異在哪?前者用於 AI 高階晶片、中介層材料是從矽轉為玻璃,而後者用於 PMIC、RFIC 等低成本晶片的成熟製程,並不需要中介層,直接透過RDL 互連。

砍掉封裝基板、BGA,CoWoP 能成為 CoWoS 下個主要路線嗎?

至於「CoWoP」(Chip-on-Wafer-on-Platform PCB),是今年新出現的先進封裝路線。

該消息來自中國媒體「華爾街見聞」,是 NVIDIA 從業 12 年的技術人員 Anand Mannargudi 在公司內部技術的簡報上的內容。目前傳出,NVIDIA 將在 Rubin GPU系列的 GR150 晶片上,同時採用 CoWoP 與 CoWoS 兩種封裝技術。

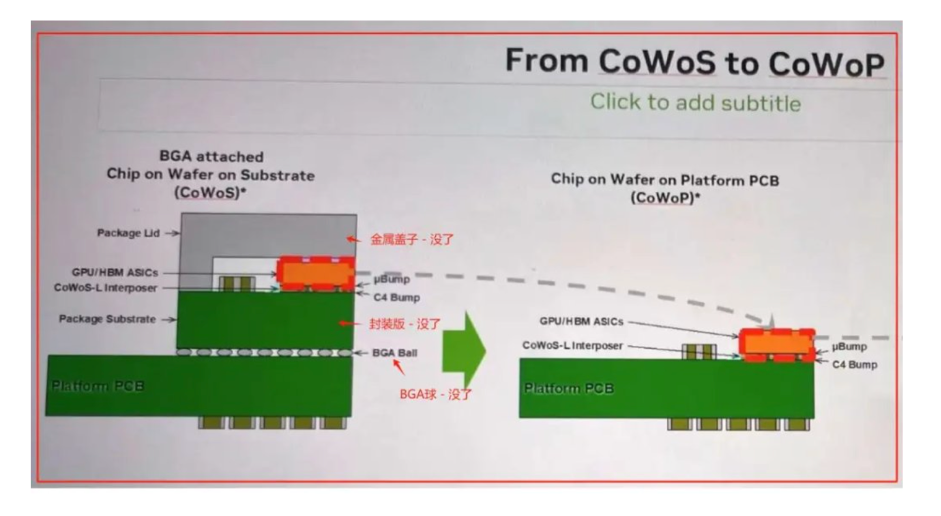

▲ CoWoP 圖示。(Source:華爾街見聞、JPM)

從圖片可知,CoWoS 包括 GPU 等邏輯 IC、HBM、中介層、封裝基板(Package Substrate),但實際上,封裝基板下還要透過 BGA(球柵陣列,Ball Grid Array)與 PCB 主機板(Platform PCB)連接。

由於 CoWoS 結構堆疊的「層級過多」,如同蓋樓一樣不斷堆疊,但當樓層越高的時候,訊號和電力要從底部傳輸到頂樓的距離就越長,損耗、成本也高。

因此,CoWoP 打算把部分樓層拿掉,即直接砍掉成本高昂的封裝基板和 BGA,並開發出技術含量較高的 PCB 主機板,使其直接承擔高精密度訊號與電源佈線,再將「晶片和中介層」這個組合直接安裝在 PCB 主機板。如此一來,晶片訊號可直接從中介層走到 PCB 主機板,使互連路徑更短、提升訊號完整性、散熱更好等。

目前 NVIDIA 正測試 CoWoP 技術中,而台系供應鏈業者也證實,取代ABF載板的 PCB主機板已正式送樣給NVIDIA進行測試驗證。

▲ CoWoS、CoPoS、CoWoP 技術進展。(Source:科技新報整理)

等等,那 WMCM 技術又是什麼?

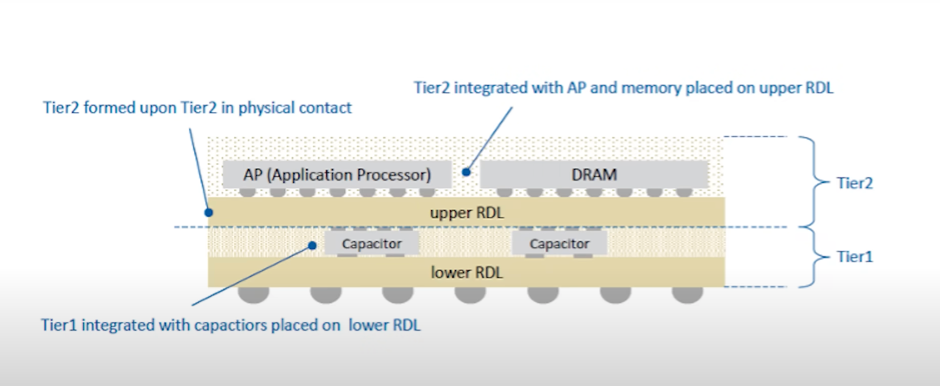

雖然這次主要都在講 CoWoS 和其延伸路線,但今年還有一個「WMCM」(晶圓級多晶片模組,Wafer-Level Multi-Chip Module)也相當值得關注,因為蘋果 2026 年將推出 iPhone 18,其搭載的 A20 處理器將使用這項技術。

據悉,WMCM 是台積電 InFO-PoP 的升級版,為台積電與蘋果共同研發、屬於「蘋果專用」的封裝技術。

InFO-PoP 是將記憶體直接堆疊在行動處理器上方,當記憶體容量增加時,散熱便成為問題。因此,WMCM 是透過將 IC 邏輯晶片與 DRAM 進行平面封裝,取代傳統上下堆疊的方式,以 RDL 取代中介層。

▲ WMCM 示意圖。(Source:投資伊森 Youtube 截圖)

由於 WMCM 使 SoC、DRAM 等不同元件在晶圓階段即整合完成,再切割為單顆晶片,因此不需要使用中介層或基板來連接晶粒,可改善散熱與訊號完整性。

▲ InFO 和 WMCM 技術比較。(Source:科技新報)

(首圖來源:shutterstock)