西門子數位工業軟體宣布推出 Tessent IJTAG Pro,透過將原本串列運作轉變為平行運作,徹底改變基於 IEEE 1687 的 IJTAG 輸入/輸出方式,同時提供自訂硬體的讀寫存取功能。

西門子指出,這款全新軟體導入高頻寬內部 JTAG(IJTAG)與通用資料串流功能,並運用西門子 Tessent 串流掃描網路(SSN)軟體的寬匯流排提升資料傳輸速度,協助客戶降低測試成本、縮短測試時間。

隨著電晶體密度在多維度上持續擴展,半導體產業正經歷前所未有的快速演進。當半導體設計從 2D 架構逐步發展至 2.5D,乃至完整的 3D IC 架構時,設計測試面臨的挑戰也呈指數級增加。測試向量數激增、向量執行時間延長、ATE 成本高漲,加上測試引腳的資源受限,若在設計流程中維持競爭優勢,優化現有基礎架構以支援測試規模擴展,更是至關重要。

西門子數位工業軟體數位設計創作平台資深副總裁暨總經理 Ankur Gupta 指出,在現今複雜的 IC 設計中,優化測試時間是一項重大挑戰。Tessent IJTAG Pro 運用西門子 SSN 架構,將傳統串列 IJTAG 運作轉換為高頻寬平行處理流程,不僅能加速測試、降低測試相關成本,還能提供革新測試存取所需的彈性,以符合產業不斷演變的需求。

Gupta 表示,隨著半導體設計從簡單的 2D 架構逐步升級至完整的 3D IC 架構,無論是單一小晶片(Chiplet)還是整個 3D IC 封裝,都能透過這款軟體節省測試成本。

Google 資深工程經理 Srinivas Vooka 指出,高頻寬 IJTAG 創新性地運用 SSN 匯流排架構,其測試向量傳輸速度遠超傳統串列方式,大幅縮短測試套用時間,在內建自我測試(BIST)與混合訊號 IP 測試方面效果尤為顯著。

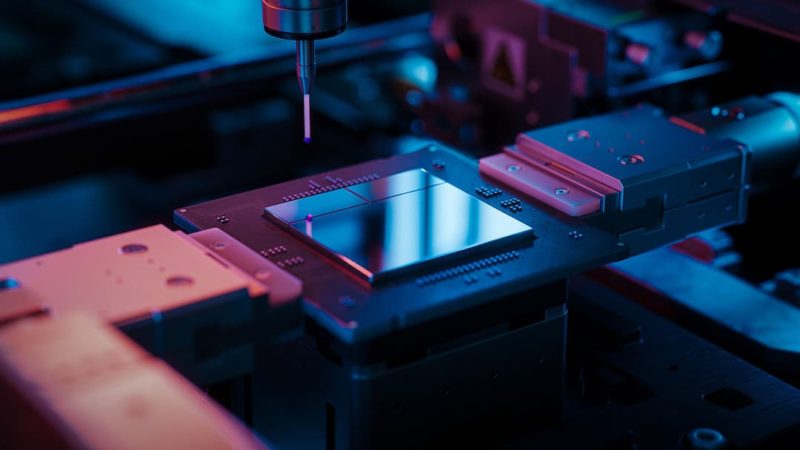

(首圖來源:西門子)