Cadence 攜手台積電擴大 AI 半導體創新,範圍涵蓋 N3、N2、A16 及 A14 先進製程 |

| 作者 Atkinson|發布日期 2026 年 05 月 12 日 10:30 | 分類 IC 設計 , 半導體 , 晶圓 |

Tag Archives: EDA

Cadence 與 NVIDIA 擴大合作,代理 AI 與數位孿生重塑半導體與 AI 工廠設計 |

| 作者 Atkinson|發布日期 2026 年 04 月 20 日 10:15 | 分類 AI 人工智慧 , Nvidia , 半導體 |

近日舉行的 CadenceLIVE Silicon Valley 2026 大會,EDA 大廠 Cadence 正式宣布與 NVIDIA 全面擴大策略合作夥伴關係。雙方合作提供涵蓋代理 AI(agentic AI)、物理模擬與數位孿生的加速解決方案,期盼釋放前所未有的生產力,並以「代理速度」(agent speed)重塑半導體設計、物理 AI 系統及超大規模 AI 工廠的新世代工程設計流程。

西門子收購 Canopus AI,將 AI 量測技術導入半導體製造 |

| 作者 林 妤柔|發布日期 2026 年 02 月 05 日 11:17 | 分類 半導體 , 晶片 |

西門子宣布收購 Canopus AI。該公司為運算及人工智慧(AI)驅動之量測解決方案的創新企業,致力於協助半導體製造商在晶圓與光罩檢測製程中,實現更高的精確度與效率。該交易已於 2026 年 1 月 12 日完成。 繼續閱讀..

Rapidus 推出先進半導體製造 AI 設計工具,支援 2 奈米 GAA 晶片生產 |

| 作者 Atkinson|發布日期 2025 年 12 月 18 日 7:30 | 分類 IC 設計 , 半導體 , 軟體、系統 |

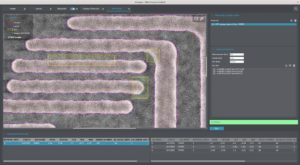

外媒報導,日本新創半導體製造企業 Rapidus 近日宣布,推出全新的 AI 設計工具套件,以支援其「Rapidus AI 輔助設計解決方案」(RAADS)。這項關鍵舉措是達成 Rapidus快速與統一製造服務(RUMS)概念的核心環節,此項技術方法 Rapidus 現已正式更名為更具主動性的 Rapidus AI 代理式設計解決方案(Rapidus AI-Agentic Design Solution,RAADS)。

加速半導體設計與測試流程,西門子推新解決方案 |

| 作者 林 妤柔|發布日期 2025 年 10 月 21 日 12:20 | 分類 IC 設計 , 半導體 |

西門子數位工業軟體宣布推出 Tessent IJTAG Pro,透過將原本串列運作轉變為平行運作,徹底改變基於 IEEE 1687 的 IJTAG 輸入/輸出方式,同時提供自訂硬體的讀寫存取功能。 繼續閱讀..

中國新凱來子公司推自主 EDA 軟體,望降低對國外依賴 |

| 作者 蘇 子芸|發布日期 2025 年 10 月 16 日 11:40 | 分類 中國觀察 , 半導體 |

綜合報導,與華為關係密切的中國半導體設備製造商新凱來科技旗下子公司啟云方,於中國《2025 灣區半導體產業生態博覽會》上正式推出兩款完全自主研發的電子設計自動化(EDA)軟體,顯示中國正加速推進晶片設計工具國產化,以降低對美歐技術的依賴。 繼續閱讀..

迎兆級挑戰!西門子 CEO:2034 年半導體產值有望達 2 兆美元 |

| 作者 林 妤柔|發布日期 2025 年 07 月 17 日 17:09 | 分類 AI 人工智慧 , IC 設計 , 半導體 |

西門子數位工業軟體旗下西門子 EDA 今(17 日)舉辦年度 IC 設計技術盛會「Siemens EDA Forum Hsinchu 2025」,由執行長 Mike Ellow 發表演講,認為現在是面對「兆級的機會與挑戰」。回顧過去,半導體產業從創立之初花約 30 年時間才達到 1,000 億美元規模;但如今,預期從 2030 年的 1 兆美元,到 2034 年將翻倍達到兩兆美元,只需要短短四年。 繼續閱讀..