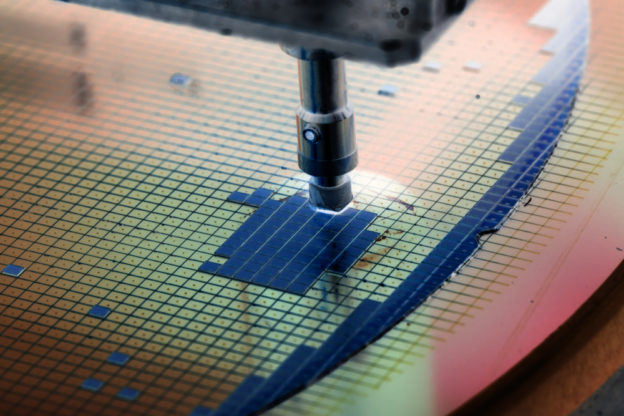

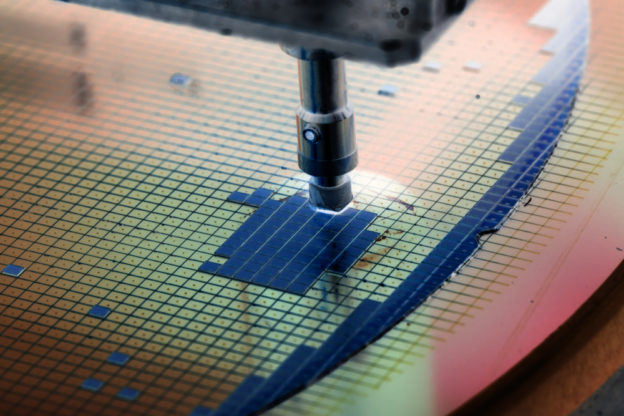

製程技術提升可能遇上瓶頸,但運算資源需求持續走高下,透過更先進設計與封裝技術提升晶片電晶體數量和運算效能就顯得格外重要。將個別製造的晶片單元整合,使單一晶片有更多電晶體的小晶片設計,無疑是提升晶片效能的良方,而 2.5D、3D 先進封裝技術則是實現小晶片設計不可或缺的環節。

本篇文章將帶你了解 :高階晶片走向多個小晶片、記憶體堆疊為必然發展趨勢 混合鍵合重要性持續上升,針對高階CIS、CPU

先進封裝持續進化,混合鍵合技術扮演關鍵角色 |

|

作者

TrendForce 集邦科技 |

發布日期

2023 年 06 月 06 日 7:30 |

分類

半導體

, 封裝測試

, 會員專區

| edit

Loading...

Now Translating...

|

製程技術提升可能遇上瓶頸,但運算資源需求持續走高下,透過更先進設計與封裝技術提升晶片電晶體數量和運算效能就顯得格外重要。將個別製造的晶片單元整合,使單一晶片有更多電晶體的小晶片設計,無疑是提升晶片效能的良方,而 2.5D、3D 先進封裝技術則是實現小晶片設計不可或缺的環節。