在 AI 晶片競爭日趨白熱化之際,龍頭輝達 (Nvidia) 為了保持領先的競爭力,據出已經獨家取得台積電即將推出的 A16 半導體製程產能。此項獨家合作不僅確保了輝達在未來晶片技術上的領先地位,同時也在先進封裝產能吃緊的情況下,凸顯了先進封裝笧能成為決定 AI 晶片供應鏈的瓶頸之一。

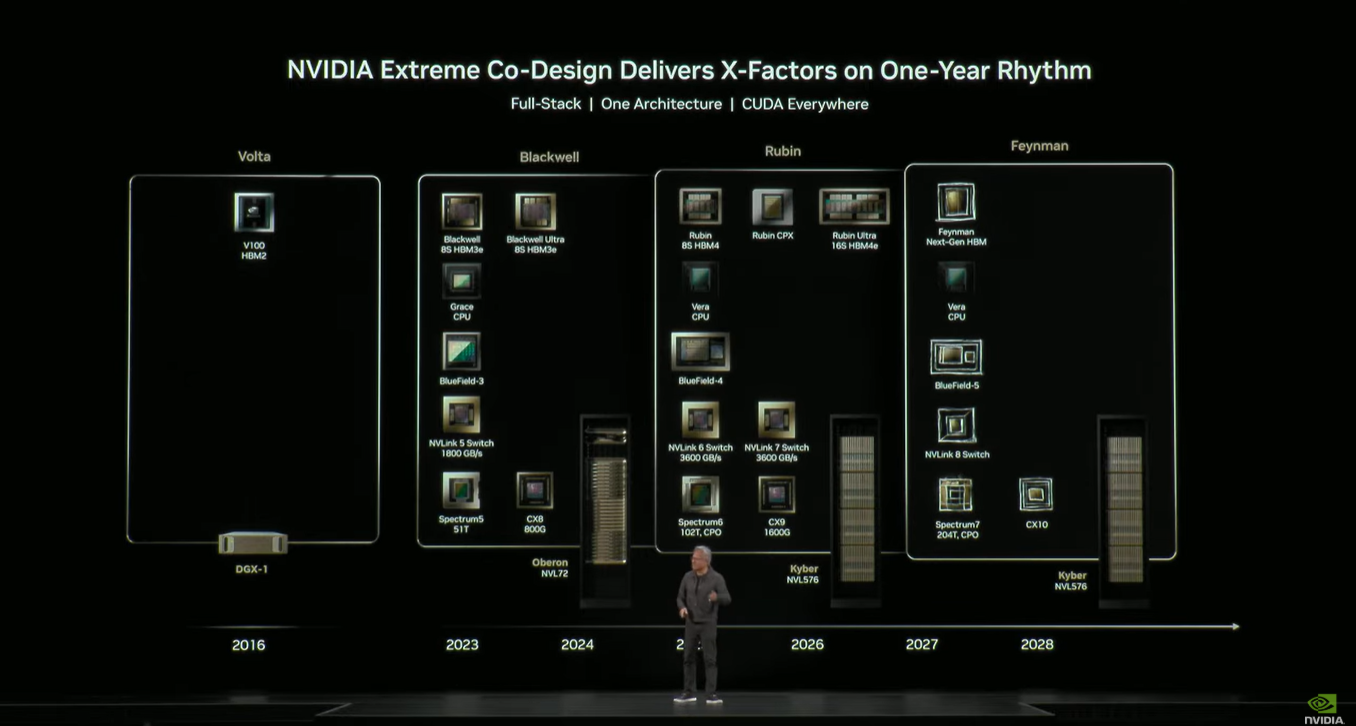

外媒報導,輝達與台積電目前正在針對 A16 製程進行聯合測試。A16 製程代表著下一代晶片技術,其特點在於採用了奈米片電晶體(nanosheet transistors)和超級電軌(Super Power Rail)技術。輝達預計將利用 A16 節點製程來生產其下一代 Feynman GPU 架構,該架構預計在 2028 年發布。

值得注意的是,A16 製程技術對 GPU 的先進封裝提出了更高的要求,當中需要更多的矽穿孔(TSV, Through-Silicon Via)通道,以具備更好的連結與散熱控制能力。事實上,先進封裝技術,特別是台積電的 CoWoS 已成為限制 AI 晶片供應的關鍵瓶頸,而輝達在此戰局中占據極大優勢。根據資料顯示,輝達在 2025 年已訂購了台積電 CoWoS-L 年產能的 70%。

在此情況下,造成台積電 CoWoS 的產能吃緊的情況下,也為委外封裝測試服務供應商(OSATs)和設備製造商創造了市場機會。為了應對這一瓶頸,台積電正積極開發替代方案,包括 CoPoS,以及計劃中的晶圓級封裝,藉新的設備和合作夥伴的加入,滿足市場龐大的需求。

另外,HBM 的供應與先進封裝同樣照控 AI 晶片的競爭格局。目前 HBM3E 的堆疊高度為 12 層。未來,HBM4 有望達到 16 層堆疊,這很可能需要使用混合鍵合(hybrid bonding)技術,特別是在 HBM4E 上。在此情況下,先進封裝的產能瓶頸就使得 HBM4 供應商緊張。

另外,面對供應鏈的限制,大型雲端服務供應商(Hyperscalers)及其晶片新創公司正受到台積電 CoWoS 供應短缺的影響。為了降低對外部供應商的依賴,業界正採取多項戰略包括建立替代的封裝生產線,以及轉向垂直整合。其中,垂直整合就代表著將設計到製造堆疊的更多環節納入自身掌控,以確保供應鏈的韌性。

總體而言,輝達透過鎖定台積電最尖端的 A16 製程,結合其在 CoWoS 產能上的巨大預留量,在下一代 AI 晶片的競爭中築起了高聳的壁壘。而產業其他參與者則必須透過創新封裝技術和實施垂直整合策略,以打破當前的供應鏈瓶頸,爭奪未來的 AI 算力市場。

(首圖來源:shutterstock)