人工智慧(AI)、高效能運算(HPC)以及大規模資料中心架構對運算能力的渴求達到前所未有的高度,半導體產業正加速向「小晶片」(Chiplet)設計轉型。半導體電子設計廠商 Cadence(益華電腦) 於近日正式宣布,第三代通用小晶片互連(Universal Chiplet Interconnect Express, UCIe)IP 解決方案已成功於台積電 N3P 先進製程技術完成投片(Tapeout)。這項里程碑不僅標誌著每通道速度達到業界領先的 64 Gbps,更為下一波 AI 創新奠定了堅實的硬體基礎。

因應 3 奈米挑戰:最佳化 PPA 與效能平衡

Cadence表示,當半導體製程演進至 3 奈米及更先進節點時,系統單晶片(SoC)設計人員面臨著極其嚴苛的挑戰。包括如何在確保高速且可靠的「晶片對晶片」(Die-to-Die)通訊之餘,同時平衡功耗、效能與面積(PPA)。

對此,Cadence 的 UCIe IP 解決方案正是為了正面回應這些挑戰而設計。該方案完全符合 UCIe 規範,並充分利用了台積電 N3P 製程的創新技術。透過這種結合,該解決方案展現了卓越的功耗效率,使客戶能夠在不犧牲效能的前提下,達成極具挑戰性的能源預算目標。在複雜的多晶片系統中,這種高效能與低功耗的結合是確保系統長期穩定運作的關鍵。

技術深度的躍進:64Gbps 頻寬與超高密度

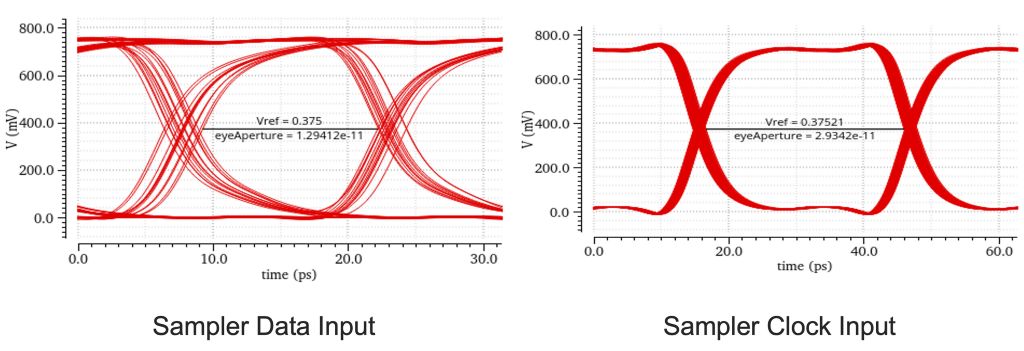

Cadence 指出,此次投片的第三代解決方案在互連技術上實現了重大進步。支援每通道高達 64Gbps 的傳輸速率,讓設計人員能夠實現超高頻寬密度,進而解鎖可擴展小晶片架構的新可能。

Cadence 強調,該解決方案在不同封裝模式下均表現出驚人的效能:

• 在標準封裝(Standard Package)中,頻寬密度達到 3.6Tbps/mm。

• 在先進封裝(Advanced Package)中,頻寬密度更是飆升至 21.08Tbps/mm。

這種針對 AI 和 HPC 應用最佳化架構,整合了同類產品中最佳的 PPA 指標,為 AI 加速器、網路設備及先進資料中心系統提供了強大的支援。

高度靈活的整合與多協定支援

為了縮短客戶的產品上市時間並降低整合門檻,Cadence 的 UCIe IP 提供了極高的靈活性。它能與多種主流介面協定無縫銜接,包括 AXI、CXS.B、CHI-C2C、PCIe 以及 CXL.io。這種多協定的支援,結合高速物理層(PHY)的完整 IP 子系統,使得該方案能迅速整合至各類平台中。此外,該架構設計強調跨供應商小晶片生態系統的互操作性(Interoperability),確保在異構多晶片環境中依然能穩定運作。

其中,在硬體層面,Cadence 導入了先進的錯誤修正(ECC)、通道邊際測試(Lane Margining)以及診斷功能,以確保在苛刻的運算環境下維持高度可靠性。值得注意的是,該方案具備自我校準(Self-calibrating)能力與基於硬體的啟動機制(Hardware-based bring-up)。這項技術突破消出了對韌體干預的需求,不僅能達到快速的系統初始化,更簡化了整體設定流程。搭配整合了鎖相環(PLL)的精簡時鐘方案,該系統在面對電壓與溫度波動時展現出強大的韌性,讓設計師能將精力集中於核心邏輯開發。

深耕與佈局:2018~2024 年演進史

事實上,Cadence 在晶片對晶片介面領域的領先地位並非偶然。Cadence 矽解決方案事業部行銷副總裁 Arif Khan 指出,公司早在 2018 年便完成了首次晶片對晶片介面的投片。而隨著產業趨勢轉向,Cadence 於 2022 年開始轉向 UCIe 標準,並在過去兩年中廣泛展示了其第一代與第二代 UCIe 解決方案的矽驗證成果。

Arif Khan 表示,鑑於 AI 與 HPC 應用對吞吐量和效率近乎無止境的需求,我們非常自豪能推出達成 64G 速度的第三代 UCIe IP。透過與長期合作夥伴台積電的協作,我們正為共同客戶提供高品質且高效的解決方案。

隨著 64Gbps UCIe IP 的成功投片,半導體產業朝著「隨插即用」的小晶片生態系又邁進了一大步。這種技術不僅解決了單一大型晶片(Monolithic SoC)在製造良率與面積上的限制,更透過異構整合,讓不同功能的晶片能以最優路徑進行溝通。這項由 Cadence 與台積電共同推動的技術創新,無疑將成為未來幾年 AI 伺服器與超級電腦研發的核心驅動力。

(首圖來源:The original uploader was King4057 at English Wikipedia. [CC BY-SA 3.0], via Wikimedia Commons)