在人工智慧(AI)時代全面爆發的當下,新世代高頻寬記憶體(HBM4)已成為支撐全球 AI 基礎設施的最核心零組件。當前,針對 HBM4 市場的主導權,全球兩大記憶體大廠──三星電子(Samsung Electronics)與 SK 海力士(SK Hynix)之間的競爭正日益白熱化。這不僅是兩家企業爭奪全球記憶體龍頭寶座的尊嚴之戰,其勝負更將深刻影響韓國經濟的未來走向。

根據韓國媒體報導,面對這場被業界比喻為「矛與盾」的激烈攻防戰,SK海力士正積極尋求HBM封裝技術的重大變革。最新消息指出,SK海力士已經擬定了一套效能躍升的祕密對策,目的是在不進行大規模製程轉換的前提下,大幅強化HBM的穩定性與整體效能,目前該項新技術正處於密集的驗證階段。

報導指出,在即將到來的HBM4規格中,產品將直接從12層堆疊起步,展現了極高的技術門檻。而為搶佔市場先機,SK海力士目前已經啟動了HBM4的首批量產作業。由於HBM4從生產到交貨的時間大約需要6個月,這代表了SK海力士此舉是為了在主要客戶輝達 (NVIDIA) 正式完成品質測試之前,採取先發制人的量產策略。

然而,要達到最高效能並非易事。業界先前一直對SK海力士HBM4的效能與穩定性下降抱有疑慮,主要原因在於NVIDIA對HBM4提出了極高的規格要求。包括單個引腳傳輸速度(Pin Speed)高達11.7Gbps,遠遠超出了該產品原先設定的8Gbps標準,這導致開發難度呈現指數級的攀升。事實上,在結合AI加速器進行的2.5D封裝測試過程中,SK海力士的HBM4確實在挑戰最高效能時遭遇了瓶頸,直到2026年初仍持續對部分電路進行改善作業,這也使得業界預估的大規模量產(Ramp-up)時程被迫稍微延後。

儘管如此,業界普遍認為SK海力士在供應NVIDIA HBM4方面出現重大波折的可能性極低。這主要歸因於當前供應鏈的現實狀況。也就是如果NVIDIA堅守極端的高規格要求,恐將嚴重限制其在2026年下半年推出最新型AI加速器「Rubin」的供應量。另一方面,目前在HBM4領域獲得回應的三星電子,考量其良率及1c DRAM的投資現況,短期內亦難以大幅擴張供應量。因此,市場指出,NVIDIA極有可能將初期採購的HBM4效能條件放寬至10Gbps等級。

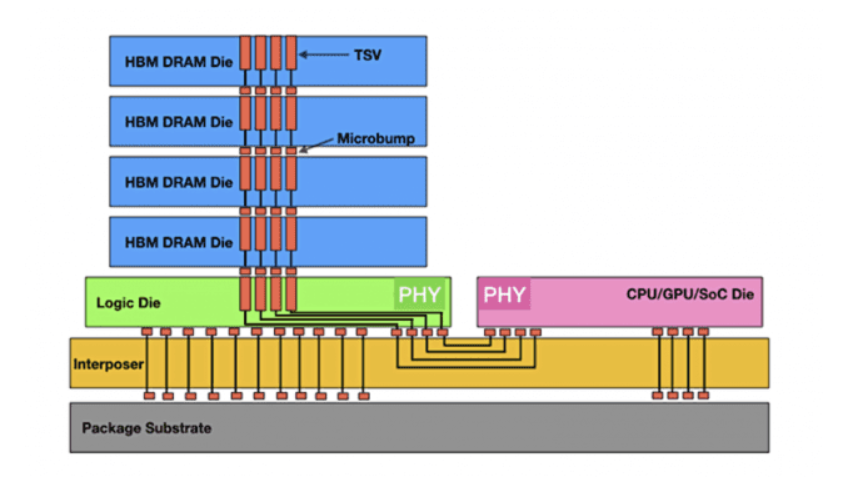

儘管供貨無虞,但正如半導體市場人士所言,HBM供應鏈不僅看重速度,更需要綜合考量良率與供應鏈的穩定性,因此SK海力士將佔據最大供應比例的預測依然有效。但為了達到最高效能,技術上的改善工作必須持續並行,這是一個不容安於現狀的時刻。市場專家指出,限制HBM4效能提升的最大癥結點在於「輸入/輸出端子(I/O)」數量的急遽擴張。在此一技術難題上,SK海力士面臨著比競爭對手更嚴苛的條件。相較於三星電子,SK海力士採用的是前一代的1b(第五代10奈米級)DRAM。同時,其底層邏輯裸片採用的是台積電(TSMC)的12奈米製程,這與三星電子(採用自家晶圓代工的4奈米製程)相比,在電路整合度上較低。這些因素都使得SK海力士在面對I/O數量增加所帶來的副作用時,顯得更為脆弱。

為了突破上述的物理與效能極限,SK海力士正將目光投向全新的封裝工法,並計畫將其應用於HBM4及未來的次世代產品中。這項被視為「秘密武器」的新技術,其核心策略主要聚焦於兩大方向,包括提升核心裸片(Core Die)厚度,以及縮減DRAM間的間距(Gap)。首先,在DRAM厚度的處理上,為了符合HBM4封裝高度必須控制在775微米(Micrometer)以下的嚴格規範,業界傳統做法是採用薄化製程(Thinning),將DRAM的背面大幅磨薄。然而,過度削薄的DRAM不僅會導致晶片效能不可逆的衰退,更會使其對外部物理衝擊的抵抗力大幅下降,極易受損。為了解決此痛點,SK海力士計劃反其道而行,將部分上層DRAM的厚度增加,以此來從根本上強化HBM4的物理結構穩定性。

其次,為了在增加DRAM厚度的同時,確保整體的封裝高度不會超出標準限制,SK海力士必須進一步壓縮各層DRAM之間的間距。這項縮減間距的工法不僅解決了高度限制,更帶來了意想不到的雙重效益。當DRAM層與層之間的距離拉近後,數據傳輸的路徑縮短,訊號傳遞速度將顯著提升;同時,從底層邏輯裸片將電力輸送至DRAM最頂層所需的能量耗損也隨之減少,大幅優化了整體的電力效率(Power Efficiency)。

事實上,這項創新技術的成敗關鍵,完全取決於「實作難度」。當DRAM層之間的間隙被極度壓縮後,要在這微小的縫隙中穩定且均勻地注入MUF(Molded Underfill,模製底部填充劑)材料,將變得極度困難。MUF在封裝結構中扮演著保護DRAM以及絕緣體的關鍵角色,如果在塗佈過程中發生不均勻,或是內部產生了空洞(Void),將會直接導致晶片報廢,嚴重打擊產品良率。

針對這項最棘手的挑戰,SK海力士已經成功研發出能夠完美克服此問題的全新封裝技術。雖然SK海力士目前並未對外公開該技術的具體細節,但其核心優勢在於:能夠在不進行大規模製程轉換、也不需要添購龐大新設備的情況下,以穩定且高良率的方式成功縮減DRAM間距。據了解,近期SK海力士內部進行的相關測試結果呈現出非常正面的數據,為該技術的量產注入了一劑強心針。

一旦SK海力士能夠迅速將這項新封裝技術推進至商業化量產階段,預期將能在HBM4以及未來的次世代記憶體產品中,極為有效地縮減DRAM間距並提升整體效能。當然,任何新技術在實際導入大規模量產時,仍有可能面臨不可預期的困難與波折。熟知此技術發展的市場權威人士對此表示,SK海力士為了突破現有HBM架構的物理極限,所精心設計的這套全新封裝工法,目前正處於非常活躍的驗證階段。這項技術最大的戰略價值在於,它允許企業在無需投入大量資本進行設備更新的條件下,實質性地改善HBM的核心效能。未來一旦成功商業化並投入市場,其對整個半導體產業鏈所產生的顛覆性效應與波及影響,絕對不容小覷。

(首圖來源:SK Hynix 提供)