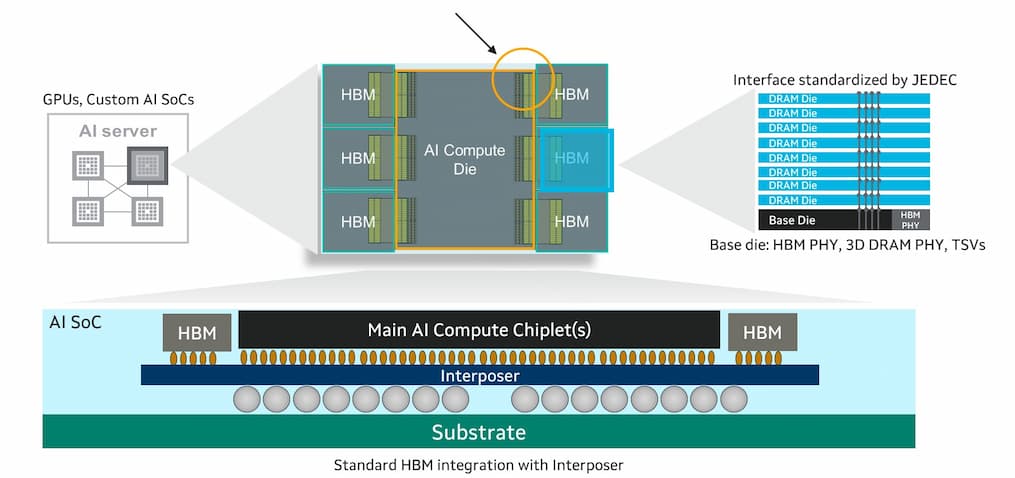

邁威爾(Marvell)在 2024 年分析師日(Analyst Day 2024)上發布針對 AI 應用的客製化 XPU 的「客製化高頻寬記憶體」(CHBM)解決方案。CHBM 與美光、三星和 SK 海力士等領先記憶體製造商合作開發,可針對特定 XPU 設計,改善效能、功耗、記憶體容量、晶片尺寸和成本。

CHBM 將與 Marvell 客製化 XPU 相容,初期不會成為 JEDEC 定義的 HBM 標準。

該公司客製化 HBM 解決方案可針對特定應用量身打造介面與堆疊,目標是減少標準 HBM 介面在處理器內部所占用的空間,釋放可用於運算和功能的空間。

Marvell 指出,藉由專屬 D2D(die-to-die)I/O,不僅能在客製化 XPU 中多裝 25% 邏輯晶片,也可在運算晶片旁多安裝 33% CHBM 記憶體封裝,增加處理器可用 DRAM 容量。該公司預期可將記憶體介面功耗降低 70%。

Breaking news: @Marvell has partnered with the leading HBM vendors with develop a custom HBM interface for faster, smaller, and lower power die2die interconnections. #Marvell2024AIDay pic.twitter.com/rnQ1ZZSox8

— Kevin Krewell (@Krewell) December 10, 2024

由於 CHBM 並不依賴 JEDEC 標準,因此硬體部分需要全新的控制器和客製化實體介面、全新的 D2D 介面及改良的 HBM 基本晶片。

根據投影片,新 Marvell D2D HBM 介面將擁有 20 Tbps/mm(每毫米 2.5 TB/s)頻寬,比目前 HBM 提供的 5 Tbps/mm(每毫米 625 GB/s)多。此外,預期無緩衝記憶體的速度將達 50 Tbps/mm(每毫米 6.25 TB/s)。

Marvell 沒透露 CHBM 介面的寬度及更多資訊,僅表示「透過序列化(serializing)與加速內部 AI 加速器晶片與HBM 基礎晶片之間的 I/O 介面,來增強 XPU」。外媒認為,與業界標準 HBM3E 或 HBM4 解決方案相比,CHBM 介面寬度較窄。

Marvell 高級副總裁暨客製化、運算與儲存部總經理 Will Chu 指出,非常感謝能與領先記憶體設計商合作,加速這場革命,並幫助雲端資料中心業者持續擴充 XPU 和基礎架構,以迎接 AI 時代的來臨。

- Marvell develops custom HBM memory solutions — interface shrinks and higher performance on the menu

- Marvell Custom HBM Compute Architecture for Custom Hyper-Scale XPUs

(首圖來源:Marvell )