近幾年半導體封裝產業正發生典範轉移(Paradigm Shift),其技術演化趨勢正從傳統的 PCB 朝向 IC 製程靠近。而目前業界公認最有機會實現超越摩爾定律的兩大技術主軸,分別是採用 2.5D/3D 立體堆疊的「異質整合(HIDAS)」封裝、以及藉由矽中介層(Silicon Interposer)互連的「小晶片(Chiplet)模組化」架構。(本文出自國立陽明交通大學材料科學與工程學系陳智教授團隊,於閎康科技「科技新航道 | 合作專欄」介紹「3D IC 封裝:超高密度銅─銅異質接合」文稿,經科技新報修編為上下兩篇,此篇為下篇。)

所謂的異質整合,廣義來說就是將兩種以上不同功能的晶片,例如記憶體與邏輯晶片、光電及電子元件、或感測器與讀取電路等,透過 2.5D/3D 晶片堆疊的封裝製程整合在一起,藉由多維度空間及多晶片互連的本質優勢,實現高效能、小體積、低耗電等整合目標。

然而異質整合雖然具有大量優勢,其成本仍然非常昂貴,如何透過優化接合條件以利於大量生產,是研究人員努力突破的方向。上篇我們已經談到銅─銅混合鍵合(Cu-Cu Hybrid Bonding)帶來的優勢。本文將進一步談陽明交通大學陳智教授團隊的研發過程,以及攜手閎康科技分析技術所達到的成果。

善用銅的特性,有望成為優異介電材料

目前混合鍵合若要用於大量生產,需要晶圓對晶圓(wafer to wafer, W2W)對接之後再切削成小塊,但 W2W 對於上下晶片的大小限制須為一樣大小,否則將有區域浪費。近年來,有學者透過各種方法希望將接合溫度與時間進一步降低,經過優化後的接合條件將有利於晶片對晶圓(Chip to Wafer, C2W)或是晶片對晶片(Chip to Chip, C2C)的大量生產。

現階段研究以 SiO2 為介電材料接合最為成熟,利用電漿的幫助即可達到低溫接合,其他種的介電材料如 SiCN、高分子等材料,皆有學者在研究當中。亦有各大學者針對銅接點的接合機制與如何降低接合溫度進行廣泛研究,由於銅最大優點為相較其他金屬材料便宜,並且具有良好的導電性、導熱性與抗電遷移特性,未來必將成為重要的接點材料。但銅在高溫下容易被氧化,表面具有氧化銅對於形成穩固的接點非常不利,目前一般的銅需要在適當真空 300℃ 至 400℃ 的環境中或是超高真空利用表面活化才能穩固接合,研究快速的銅─銅直接接合接點對於大量生產非常重要。

目前銅接點最好用的方法為熱壓接合法(Thermal Compression Bonding),為了達到低溫接合,學者研究出了以下幾種方法,第一種為接合前在銅接點表面鍍上一鈍化層(Passivation Layer),防止銅氧化物生成來達到低溫接合,常用的鈍化金屬有銀 [9]、金 [10] 與鉑 [11] 等。另一種方式為改善接合表面擴散係數來達成低溫接合。

2012 年陳智教授團隊發現以直流電鍍方式可以製備出奈米雙晶銅 [12],透過儀器分析其表面具有高度(111)的優選方向,在 2014 年報導利用高度(111)的優選表面在 150℃ 持溫 60 分鐘即可完成接合 [13]。經過進一步的研究發現,具備高優選(111)表面的銅可以大幅提升表面的擴散係數,使銅接點可以在低溫或短時間內將界面孔洞消除形成穩固的銅接點;並且由氧化實驗中發現,表面為(111)方向時表面氧化物會較其它晶面少 [14],其原因為在面心立方堆積結構中,(111)晶粒表面有最少的斷鍵,較不易生成氧化物。

團隊在 2019 年進一步將奈米雙晶結構備製成銅凸塊,並在 300℃、壓力 90MPa 條件下只需要 10 秒即可以完成接點的接合,並且獲得可靠的接點強度 [15],將其稱為瞬時接合(Instant Bonding)。此接合條件雖然溫度仍有點高,但可以在 10 秒內完成一個晶片的預接合對於未來 C2W 或是 C2C 接合將會有非常大的幫助,可以大幅減少接合成本。2021 年陳智教授團隊也成功完成奈米雙晶銅/SiO2 的混合鍵合 [16],溫度控制在 200℃ 即可以完成接合。

熱壓接合四階段

陳智教授團隊將熱壓接合分成以下四階段,每一階段以孔洞的變化與銅接點微結構來區分,圖八為四個階段的流程圖。第一個階段為「塑性形變」主導範圍,初期銅接點表面有非常多的凹凸處,接觸面積少,故施予的下壓力非常容易超過金屬的降伏強度(Yield Strength),這些區域會在短時間內因塑性形變縮小接點間的間隙,此時接觸部分應該會介於晶界與表面之間的一種狀態,我們將之稱為類晶界(Quasi Grain Boundary),未接觸的部分則會呈現不規則形狀的孔洞。

第二階段為由「潛變」主導的階段,接合比例隨著塑性形變發生而降低,其壓應力會降至降伏強度以下,此時雖然低於降伏強度但是材料仍處於一個下壓力,將導致接點的接合處與孔洞處產生應力梯度(Stress Gradient),此應力梯度會讓銅原子擴散並持續縮小孔洞大小,且表面銅原子與對面銅原子會開始形成金屬鍵,讓類晶界慢慢轉變成為界面晶界(Interfacial Grain Boundary)。2021 年,團隊建置出一個擴散模型,計算出了此階段接合時間(tbonding)如式子 1 [17],由式子 1 可以知道接合時間與表面粗糙度(Rq)、接合溫度、下壓力及有效擴散係數(Deff)有關係。由於接合機制在初期階段是由表面擴散主導、而後期則轉變成晶界擴散主導,此將使得有效擴散係數的數值大小界於表面擴散係數與晶界擴散係數之間。此外,當接合比例越來越大、或是轉變成晶界擴散時,潛變形變速率將會大幅降低,且經過此階段後,界面也將殘留大小不一的孔洞。

接著進入第三階段:「孔洞熟化」(Void Ripening)階段。於此階段開始出現較大孔洞成長與較小孔洞縮小的現象,原因是此階段的孔洞為了降低整體能量,小孔洞具有較大的吉布斯自由能(Gibbs free energy)而較不穩定,空孔會由小孔洞沿著界面晶界往大孔洞移動,導致孔洞熟化現象發生,使平均孔洞尺寸變大 [18]。最後一階段為「界面消除」階段,界面晶界受到晶粒成長影響而被消除掉,孔洞會被留在晶粒內部,空孔擴散的路徑會由晶界擴散改變成晶格擴散(Lattice Diffusion),致使空孔的擴散速度大幅下降,此時孔洞的大小將難以改變,其平均尺寸將不會有太大的變化。

▲ 圖八、接合步驟流程圖。

接合後對於接點的分析非常重要,目前常見的非破壞分析方式為使用超音波掃描顯微鏡(Scanning Acoustic Microscope, SAM)來確認接合是否成功,藉由超音波穿透接合試片檢查接點是否存在間隙,若有間隙存在則為接合失敗區域,可再考慮以超高解析度 3D X-Ray 顯微鏡來進一步接點觀察。以上兩種分析方法,其影像解析度僅能達到數十微米至 1 微米左右。然而,在利用破壞性分析手法(聚焦離子束)初步觀察後可以確認,實際接合界面會存在數十奈米的小孔洞,欲單純採用非破壞性的分析方式,實難以觀測到所有的界面孔洞。因此,目前對於接合面孔洞檢測作法大多是採用破壞性分析。然而,此針對接點橫切面進行電子顯微鏡影像分析之作法仍有不足之處,其能夠觀測到界面孔洞數量非常有限,無法真實呈現接合處的孔隙結果。

全新觀測方式,掌握銅─銅超高密度接合孔洞

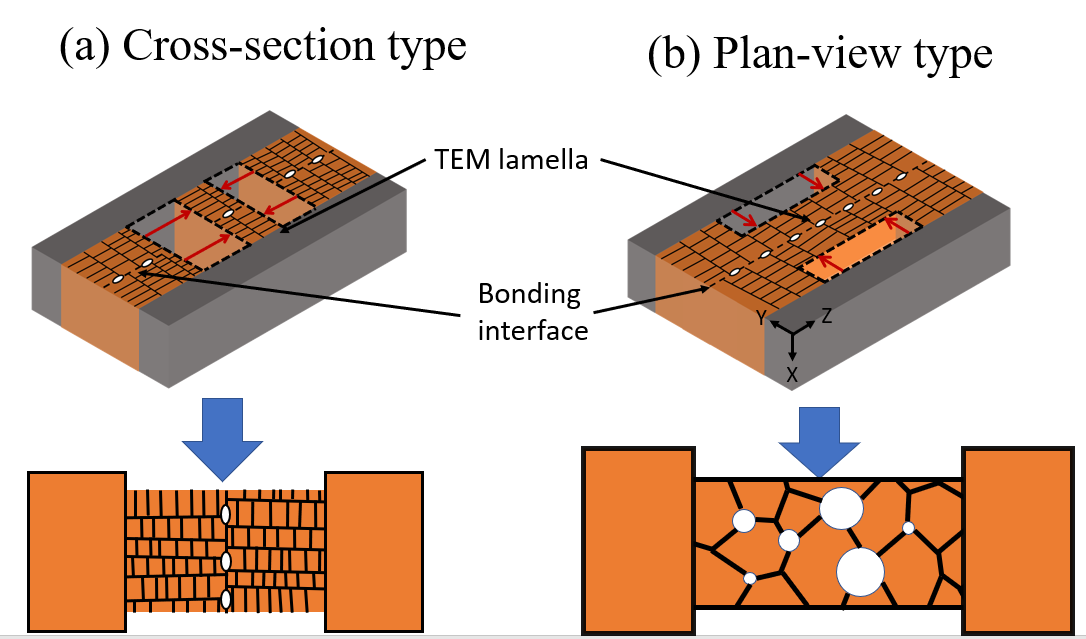

陳智教授團隊與閎康科技(Materials Analysis Technology Inc., MA-tek)共同研發出新的銅接點界面觀測方式,其中一種為使用穿透式電子顯微鏡(TEM)薄片備製方法、如圖九所示,稱之為 Plan-view Type。此作法首先將接合界面完整地挖出,整個薄片皆為接合界面,再利用電子顯微鏡觀測及拍攝接合界面的俯視圖,並測量統計界面孔洞的數量與大小。

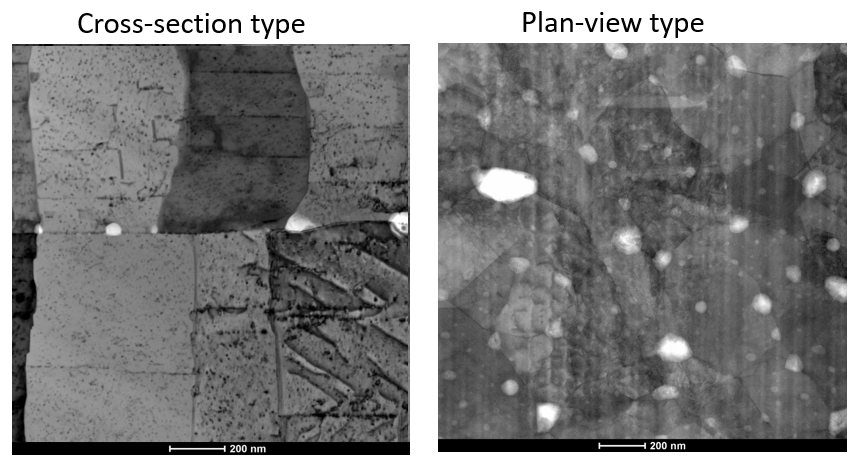

圖十所示之影像範例是以 Plan-view Type 分析接合界面的實際結果。相比於一般橫截面(Cross-sectional Type)作法,Plan-view Type 不僅可藉由觀察界面俯視圖,在小範圍內觀測到更大量的孔洞,並且能分析的孔洞尺寸範圍也更大、約落在 10 至 100 奈米之間,此對於孔洞的研究幫助非常大。第二種方法為使用聚焦式離子顯微鏡系統搭配高解析度掃描式電子顯微鏡來觀測孔洞,我們稱之為 Cut and View,分析作法如圖十一所示。

此方法較適合分析接合界面孔洞尺寸稍大(至少大於 70 奈米)的試片。隨著離子束切削時掃描式電子顯微鏡持續拍攝,可以每隔一小段距離就拍攝一張照片,將所有照片製作成疊圖後,即可以確認所有孔洞的數量與大小。以上兩種分析方法在未來皆非常的重要,目前混合鍵合的接點尺寸可以小於 1 微米以下,因此對於接點的分析通常需要借助電子顯微鏡的幫助,而上述分析方式將可以有效地觀察銅接點內部孔洞。

▲ 圖九、銅接點利用穿透式電子顯微鏡薄片備製方式觀測孔洞兩種方式。

▲ 圖十、相同條件銅接點利用穿透式電子顯微鏡薄片備製方式觀測孔洞兩種方式區別。

▲ 圖十一、Cut and view 分析方式示意圖。

銅─銅混合鍵合技術可實現超高封裝密度,並提供優異的導電與導熱性質,預期在近年內它將會被大量地應用於高速計算元件中(High Performance Computing)。然而,此技術製程良率仍有待提升,並且其在結構可靠度方面,例如電遷移、溫度循環測試等的相關研究資料也還不多,需要業界與學界共同投入更多的資源來加速發展。

展望:異質整合的技術進展與企業布局

回頭審視異質整合的各項封裝技術。2.5D 封裝的基本概念,是利用矽晶圓製作的一片矽中介板,將數個功能不同的晶片以並排或堆疊的方式放在板子上,相互連接形成特定的功能模塊,再將一個或數個功能模塊與 PCB 基板封裝在一起。該矽中介板通常具有矽穿孔(TSV)結構,可提供微小間距的正反面接點訊號連結;而晶片與矽中介板、及矽中介板與 PCB 基板之間,則分別以微凸塊(Micro Bumps)及焊錫凸塊(Solder Bumps)相互連接。

目前較為人熟知的 2.5D 封裝技術,是 TSMC 發展多年的 CoWoS (Chip On Wafer On Substrate)架構,TSMC 於 2016 年以此技術擊敗當時競爭對手 Samsung,取得 Apple iPhone 7/7Plus 手機的 A10 處理器訂單,首度向外界展示了其在先進封裝領域的技術實力。

除此之外,扇出型晶圓級封裝(Fan-Out Wafer Level Packaging, FOWLP)也是 2.5D 封裝的主流技術之一。FOWLP 技術原是由德國 Infineon 所開發,其可在相同封裝尺寸條件下,讓重分佈層(Redistribution Layer, RDL)範圍更廣、引腳數更多、整合更多功能;最重要的是,該技術無需使用封裝載板(不用打線或焊錫凸塊)。FOWLP 能取代成本較高的 TSV 製程,提供先進晶片所需要之高密度訊號接點,藉此降低約 30% 製程成本,同時也讓晶片更薄。根據研究機構預測,未來每支智慧手機中使用 FOWLP 技術的晶片將超過 10 顆,所生產的晶片數量成長率可達 32%,甚至在 2020 至 2026 年應用市場的複合成長率將會達到 15.1%。

所謂 3D 封裝技術,目前大多應用於提升 HPC 晶片的運算效能,其常見於高頻寬記憶體(HBM)與 CPU、GPU、FPGA、或 NPU 等處理器彼此間的晶片整合。3D 封裝通常是藉由 TSV 互連技術將所有晶片垂直疊合在一起,減小彼此間的傳輸路徑,提高整體晶片的運算速度及能力。目前較知名的 3D 封裝技術,如 TSMC 提出的 SoIC 整合封裝架構,其主要利用 W2W 及 C2W 的混合鍵合技術,實現 10um 以下 I/O 節點互連、減少寄生效應、並使晶片更薄等封裝功效。

Samsung 則於 2020 年推出名為 X-Cube 的 3D 封裝技術,藉由該技術將 4 顆 SRAM 堆疊在邏輯核心運算晶片上,並透過 TSV 結構進行連接。X-Cube 封裝已成功應用於 7nm EUV 製程,並在次世代 5nm 製程進行驗證,未來應用將鎖定在 HPC、5G、AI 等高階領域。

Intel 的布局也不惶多讓,於 2018 年底推出名為 Foveros 的 3D 邏輯晶片封裝技術,透過 TSV 與 Micro Bumps 將不同晶片以 Face-to-Face 方式堆疊連接。目前 Foveros 技術能使凸點間距達到 50um,未來有望縮減到 10um,讓凸點數量達到每平方毫米 10,000 個。如此高密度的接點,可使多晶片整合時無須再考慮 Fan-in 和 Fan-out 結構設計。此外,Foveros 封裝也同時具有高度可擴展性,融合了自家 2D/3D 封裝的兩大核心技術 ODI 和 CO-EMIB,使所有封裝整合的小晶片之間,彼此實現全方位的訊號互連。

展望:小晶片技術的進展與企業布局

至於 Chiplet 的模組化封裝架構,簡單來說就是將多個較小的同質或異質晶片,整合組成單一個大晶片。其作法是將原來設計在同一個 SoC 晶片中的電路元件,分拆成許多不同區塊的小晶片,再藉由先進封裝製程整合在一起。相較傳統 SoC 系統單晶片將所有的元件設計放在單一顆裸晶上,Chiplet 封裝架構可將大尺寸的多核心設計分散到個別的小晶片上,提升晶片在功能整合設計上的靈活性,也能獲得更好的製程良率、更低的成本優勢,減少設計時程以加快產品上市時間。

Chiplet 的封裝架構最早由 Intel 和 AMD 公司所提出,概念類似於樂高積木的基礎模塊,具有很好的通用性,可將各個小晶片靈活組建成不同的 IP 模型。因此,若該封裝架構有產業標準化的互連通訊規範,將可在設計高階 SoC 晶片時,直接以 IC 設計公司所提供的 Chiplet 晶片 IP 模組來進行組合設計與製造。

目前 Chiplet 封裝技術的開發仍處於早期階段,有鑑於未來應用市場的無限可能,2022 年 3 月 Intel 聯合了包括 ASE、AMD、ARM、Google Cloud、Meta、Microsoft、Qualcomm、Samsung 與 TSMC 等多家公司,宣布共同成立 Chiplet 產業聯盟,制訂小晶片間通用元件的互連傳輸標準 UCIe (Universal Chiplet Interconnect Express),加速建立開放式的全球 Chiplet 封裝生態系統。

結語

隨著半導體線寬縮微已逼近物理極限、摩爾定律發展難以為繼,全球晶圓代工大廠的發展重心逐漸從過去追求更先進的晶圓製程,轉向於封裝技術之創新。本系列上下篇文章,即是針對先進封裝應用中最具優勢的製程技術「銅─銅混合鍵合」進行全面性介紹。陳智教授 1999 年自美國加州大學洛杉磯分校 UCLA 材料系取得博士學位後,便於陽明交通大學材料系任教及研究,目前擔任系主任職務,是學術界發現(111)奈米雙晶銅的先驅。其研究成果於 2012 年發表在頂級期刊科學雜誌《SCIENCE》。而隨後也將該成果技轉給台灣國內廠商並成功量產,實質幫助本土公司進入電鍍銅添加劑市場。陳智教授多年來對於學研領域有相當卓越之貢獻,屢獲國內外多項大獎的肯定,同時也於 2020 年獲選為國際先進材料學會(IAAM)會士。而閎康科技由於擁有完備的檢測設備與專業技術經驗,能全面滿足電子材料、製程及封裝方面之各種分析檢測需求,因此與陳智教授攜手進行產學合作,提供該團隊在低溫銅─銅接點製程研究上所需之完整分析服務技術。

延伸閱讀:

參考資料:

[9] Chou, Tzu-Chieh, et al. “Electrical and reliability investigation of Cu-to-Cu bonding with silver passivation layer in 3-D integration." IEEE Transactions on Components, Packaging and Manufacturing Technology 11.1 (2020): 36-42.

[10] Wu, Yu-Ting, and Chih Chen. “Low temperature Cu-to-Cu bonding in non-vacuum atmosphere with thin gold capping on highly (111) oriented nanotwinned copper." Journal of Electronic Materials 49.1 (2020): 13-17.

[11] Liu, Demin, et al. “Investigation of low-temperature Cu–Cu direct bonding with Pt passivation layer in 3-D integration." IEEE Transactions on Components, Packaging and Manufacturing Technology 11.4 (2021): 573-578.

[12] Liu, Tao-Chi, et al. “Fabrication and characterization of (111)-oriented and nanotwinned Cu by DC electrodeposition." Crystal Growth & Design 12.10 (2012): 5012-5016.

[13] Liu, Chien-Min, et al. “Low-temperature direct copper-to-copper bonding enabled by creep on (111) surfaces of nanotwinned Cu." Scientific reports 5.1 (2015): 1-11.

[14] Tseng, Chih-Han, King-Ning Tu, and Chih Chen. “Comparison of oxidation in uni-directionally and randomly oriented Cu films for low temperature Cu-to-Cu direct bonding." Scientific reports 8.1 (2018): 1-7.

[15] Shie, Kai Cheng, Jing-Ye Juang, and Chih Chen. “Instant Cu-to-Cu direct bonding enabled by< 111>-oriented nanotwinned Cu bumps." Japanese Journal of Applied Physics 59.SB (2019): SBBA03.

[16] Ong, Jia-Juen, et al. “Low-Temperature Cu/SiO2 Hybrid Bonding with Low Contact Resistance Using (111)-Oriented Cu Surfaces." Materials 15.5 (2022): 1888.

[17] Shie, Kai-Cheng, et al. “A kinetic model of copper-to-copper direct bonding under thermal compression." Journal of Materials Research and Technology 15 (2021): 2332-2344.

[18] Liu, Hung-Che, et al. “Interfacial void ripening in CuCu joints." Materials Characterization 181 (2021): 111459.

(首圖來源:Created by Freepik;資料來源:閎康科技)