為滿足未來高效能運算需求,3D-IC 堆疊與小晶片異質整合方案成為延續摩爾定律的主要解決方案,許多廠商也對這項技術躍躍欲試。對此,電子設計自動化(EDA)工具與半導體 IP 供應商益華電腦(Cadence)領先業界推出全新「Integrity 3D-IC平台」,幫助客戶在 3D-IC 設計流程更容易。

「我們的目標是讓 3D-IC 變得非常簡單。」Cadence Sr. Software Architect 資深處長趙佑錫表示,許多客戶其實對 3D-IC 很感興趣,但有兩大考量成為阻礙,一是成本,二是不知從何下手。

▲ Cadence Sr. Software Architect 資深處長趙佑錫。(Source:Cadence)

趙佑錫指出,3D-IC 成功的關鍵是「並行設計」,設計流程需要不同領域技能及跨團隊合作,像封裝(packaging)、設計劃分(partitioning)、設計實現(implementation)、晶片實現和分析(analysis)都由不同部門執行,因此優化跨工具才能使流程更有效率。換言之,必須克服跨流程、跨越工具,實現共同優化等重重阻礙,才能解決 3D-IC 的設計挑戰。

3D-IC 設計挑戰 1:缺標準化設計流程,只能仰賴工程師經驗

傳統作業流程是初期團隊完成現階段工作後,再交給下一棒團隊處理,當出現問題時都「硬著頭皮解決」,若前期設計不夠完善,後續可能為解決問題而犧牲掉晶片性能。

趙佑錫表示,目前部分大公司已製造出 3D-IC,顯示這項技術確實可行,但仍面臨缺乏標準化設計流程,一切必須依靠工程師經驗,也導致產生「大公司才有資源實現這些晶片」的思維。「我們的任務是讓 3D-IC 設計及流程變更容易,尤其是對小公司而言。若小公司接受代工廠提供的 3D-IC 製程考量,設計就可交由 Cadence 解決」。

趙佑錫指出,Cadence Integrity 3D-IC 平台將所有需求整合到統一平台中,涵蓋晶片、基板、封裝、電路板及與系統設計等架構階段,及晶片實現相關的封裝、設計劃分、設計實現和分析流程。

同時,Integrity 3D-IC 平台也是業界唯一滿足所有最新台積電 3DFabric 認證的完整解決方案,「目前只有 Cadence 有這個能力」,公司需要確保所有客戶都可以使用 3D-IC 設計方法。此外,在 Cadence 解決方案中,從Cerebrus AI到 Integrity 3D-IC 環境中,全賦予異質整合技術能力,不管同質、異質都考量到支援這樣的需求。

3D-IC 設計挑戰 2:流程涵蓋範圍廣,哪個因素該優先考量?

除了流程上須跨團隊合作外,3D-IC 設計本身也相當困難,尤其是流程的涵蓋範圍。成功 3D-IC 設計需要工具包括全客製化和數位化對晶片/基板/封裝/電路板、設計劃分與設計實現,並針對時序、壓降、熱、機械、封裝以及效能、功耗與面積(PPA)進行系統級實現和分析。

然而,IC 設計人員往往會遇到兩個問題:先從哪個設計環節下手?該先權衡(Trade-off)哪項因素?

趙佑錫解釋,在第一個挑戰中,IC 設計人員必須一次考量到功能模組在晶片上該如何配置、各個位置的電壓需要多少、凸塊(bump)如何規畫排列、記憶體該放置在何處,「哪個要先當首要考量?誰是第一棒?很難協調清楚」。

第二個挑戰是設計人員面臨許多權衡問題,例如期望熱分析表現好,但設計擺放上就會傷害到壓降(IR);又或者,想增加堆疊數,但又影響矽晶片尺寸,犧牲掉良率、光罩價格和成本。

一旦這些權衡、客戶問題點全都整合進設計時,就會耗費許多時間在工程師、團隊、客戶間來回修正,因此「導入 AI,實現共同優化」才是解決這些難題的途徑。

AI 實現共同優化,加速設計流程

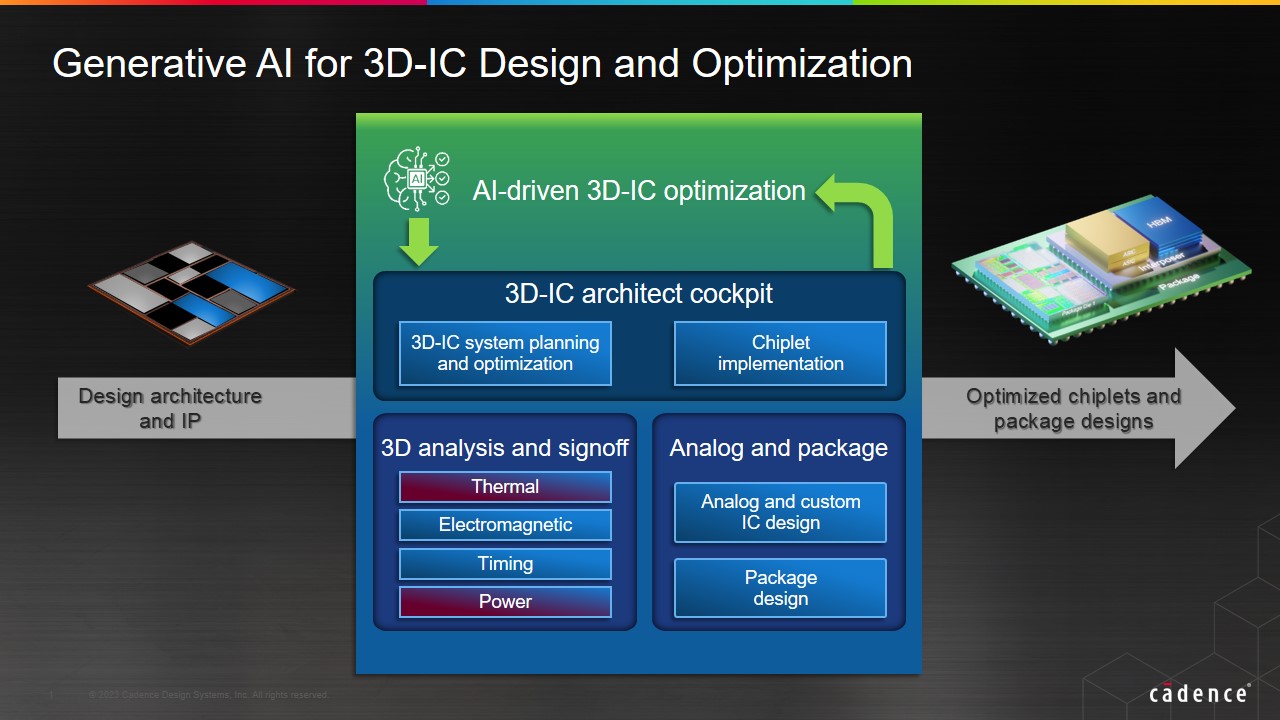

趙佑錫表示,Cadence 已使用 Cerebrus AI 驅動設計優化技術,將生成式 AI 功能整合進 Integrity 3D-IC 中;透過生成式 AI 和增強型機器學習,提供多參數、多目標的 AI 優化方案。

▲ Cadence Integrity 3D-IC 可透過生成式 AI 和增強型機器學習,提供多參數、多目標的 AI 優化方案。(Source:Cadence)

Integrity 3D-IC 將系統級規格轉化成硬體描述語言的架構,經驗上以凸塊規劃作為突破口,納入客戶需求,透過 AI 自動產生各種凸塊排列組合,作為引導設計劃分、模組布局,之後 AI 持續生成最佳解,包括提供早期的壓降和熱分析,並一次性共同優化,同時以賞罰機制加強 AI 學習,再選擇最佳衡權的多種解決方案,滿足 3D-IC 設計目標。

趙佑錫解釋,這有助於減少修改架構來回或重新設計的時間,生產力(Productivity)至少增加 10~20 倍,「以往架構完成需要 7~8 個月,但導入 AI 後可以將時間縮減至 2 個月以內,加強工程師的生產力」。客戶只需填寫一個表格或表單,就能讓 AI 自動生成出多種不同的晶片架構設計。

與晶圓代工廠合作,加速流程標準化

為使 3D-IC 成功,EDA 供應商與代工廠密切合作至關重要。當代工廠和 3D-IC 成本下降,客戶才有機會接受這些解決方案,如果製程或 3D-IC成本過高,客戶無法製造 3D-IC 晶片,採用也將受限。

除了同一製程節點內晶片的同質 3D 整合外,異質 3D 整合還要求工具和流程能對一個節點與另一個節點的不同物理屬性進行建模和分析,加劇 EDA 設計實現和系統分析挑戰。對此,Cadence 與領先晶圓廠合作,定義晶片設計人員可使用的 3D-IC 方法,包括建立標準資料交換格式,讓業界彼此間互相交換,以及可重複使用、在 3D-IC 晶片之間使用的分析模型。

趙佑錫指出,Cadence 在生成式 AI 的研究發展及應用,獲得實質性大躍進,而結合 Cerebrus AI 和 Integrity 3D-IC 工具,也是 Cadence 產品的獨特優勢。

目前 Integrity 3D-IC 平台為已將設計領域/學科中Cadence系統規劃、晶片和封裝實現以及系統級分析整合在單一平台的整合解決方案,解決客戶經常面臨的 3D-IC 設計挑戰,實現創新設計。

(首圖來源:Shutterstock)