根據外媒報導,隨著半導體製程技術持續向 2 奈米(2nm)及更先進節點推進,全球晶片產業正迎來一場結構性的典範轉移。過去單純依賴電晶體微縮(Scaling)來提升效能的時代已經結束,取而代之的是透過「小晶片(Chiplets)」技術進行異質整合、更精細的電源與熱管理策略,以及對良率與可靠性的全新定義。這場變革不僅重塑了晶片設計的規則,更深刻影響了從晶圓代工、封裝測試到終端系統整合的整個供應鏈。

製程微縮新常態,不再是「一體適用」

半導體產業長期奉行的 PPA(效能、功耗、面積)與成本(C)指標依然是核心,但在 2nm 世代,這些指標的權重與實踐方式出現了顯著分歧。過去,市場主要劃分為智慧型手機的極低功耗晶片,以及伺服器的高效能晶片。然而,隨著人工智慧(AI)滲透至各類電子產品,應用需求變得極度零碎化。

Lam Research(科林研發)公司副總裁 David Fried 指出,在 2nm 世代,複雜的整合系統中可能只有少部分元件真正需要採用最先進的製程節點。這是一種「最佳化」的過程-過去產業界致力於將所有功能整合在單一晶片(Monolithic SoC)上以優化 PPA/C;如今,先進封裝技術允許工程師針對個別子系統進行優化。

這種轉變促成了「解構(Disaggregation)」的趨勢。透過將不同的處理器與功能拆解為多個裸晶(Die),設計者可以根據功能需求選擇最合適的製程節點,而不必強行將所有元件都擠在昂貴的最先進節點上。這不僅能簡化應對非關鍵元件短缺時的備案流程,更能將有限的先進製程產能保留給最關鍵的邏輯運算單元。

去整合化與異質整合的崛起

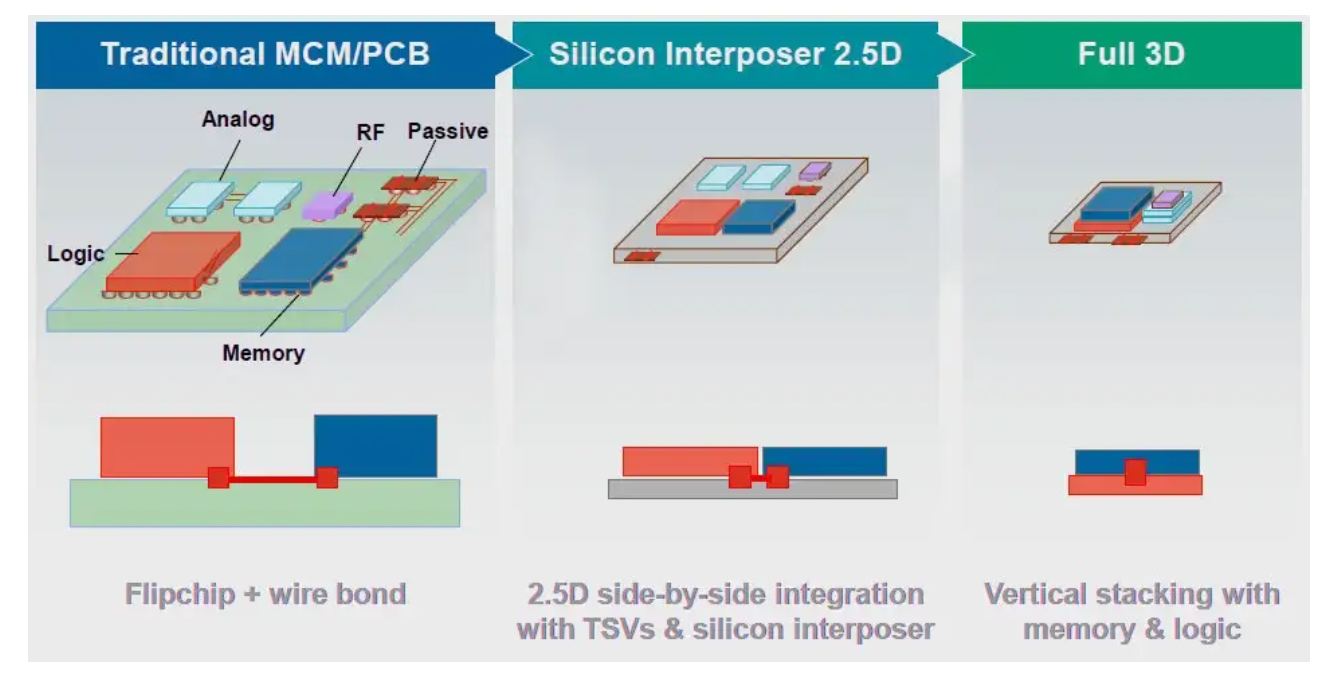

「今天,許多應用程式正透過『去整合化(De-integration)』來獲得優化,」David Fried 解釋道。這代表著邏輯電路與記憶體分離、I/O 與邏輯分離,甚至記憶體控制器也與記憶體本身分離。這種朝向複雜先進封裝流程的移動,正是當前產業優化 PPA/C 的主流路徑。

日本晶片製造商 Rapidus 的封裝技術領域技術長 Rozalia Beica 表示,這對供應鏈帶來了廣泛的影響。Rapidus 雖然獲得了 IBM 的 2nm 技術授權,但他們是專注於提供 2nm 小晶片,並計畫與其他晶圓代工廠或封裝測試廠(OSAT)合作,將其他非 2nm 的技術(如 4nm 或 7nm)整合到同一個封裝中,這種靈活性與客製化能力將是未來的關鍵。

Synopsys(新思科技)工程副總裁 Abhijeet Chakraborty 進一步指出,即便是單一晶片內部的標準單元設計也出現了「混合搭配」的概念。設計者可以混合使用高效能、低功耗或高密度的標準單元。如果為了追求極致效能而全部使用高效能單元,可能會在功耗或其他指標上付出代價,因此 EDA 工具必須能夠明智地選擇組合以最大化效益。在多晶片模組中,甚至可以看到 28nm 晶片與 2nm 晶片混合使用的場景,這成為降低成本與良率門檻的有效手段。

熱能與功率密度成為物理極限的挑戰

然而,邁向 2nm 的道路並非坦途。隨著電晶體密度在 2nm 製程下進一步提升,功率密度(Power Density)隨之增加,這引發了嚴峻的熱管理問題。即便每一代新製程通常能在特定工作負載下節省功耗,但如果晶片的使用率(Utilization)過高,產生的熱量將難以從晶片內部導出。這可能迫使系統必須採用更複雜的冷卻方案,或者透過「效能節流(Throttling)」來降溫,但後者會抵消升級至 2nm 原本應帶來的效能優勢。

從 20nm 節點開始,熱問題就日益棘手。FinFET 技術雖然減少了閘極漏電,但更高的電晶體密度增加了熱密度。到了 2nm 採用的環繞式閘極(GAA)技術,雖然預期能再次改善閘極漏電,但在高邏輯使用率下的功率密度問題依然存在。這意味著,未來的高階晶片設計必須在多晶片組件中進行複雜的權衡,決定數據應該在系統的何處進行處理或預處理,以避免熱失控。

晶片效能成長邊際效益遞減

另一個殘酷的現實是,過去每個新節點帶來「效能提升 30%、功耗降低 30%」的時代已不復返。Synopsys 的 Chakraborty 預估,客戶從 3nm 轉向 2nm,預期平均能獲得 10% 至 15% 的效能提升,以及 20% 至 30% 的功耗降低,電晶體密度則提高約 15%。雖然低功耗對於追求「每瓦效能(Performance per Watt)」的應用極具吸引力,但要實際達成這些指標面臨著製造與良率的現實挑戰。

Intel 邏輯技術開發副總裁 Ben Sell 也證實了這一趨勢。他指出,Intel 在 2026 年 1 月推出的 Panther Lake 處理器採用了 18A 製程(相當於 1.8nm),其設計核心重點在於每瓦效能與面積微縮,而非單純的原始效能。Panther Lake 採用了運算小晶片(Compute Tile)搭配其他功能小晶片的設計,針對圖形處理或介面連結等不同需求,分別優化其功耗與效能的權衡。

動態管理就夠良率與可靠性的新定義

在 2nm 與 18A 時代,確保晶片正常運作的挑戰已超越了單純的電晶體微縮。proteanTecs 技術長 Evelyn Landman 指出,現在的主要挑戰是「全生命週期的不確定性管理」。因為,隨著架構轉向奈米片(Nanosheets)與新的供電方案,元件物理、製造、封裝及實際工作負載之間的容錯空間急劇縮小。

局部電壓下降、熱梯度、老化及工作負載引發的應力等效應,不再是次要因素,而是被持續放大。Landman 強調,靜態的假設與最壞情況的「安全餘裕(Guard-bands)」已不再適用,因為最危險的情況往往是動態的、依賴於工作負載的。未來的贏家將是那些能夠在晶片生命週期中,動態且連續地監測並管理這些安全餘裕的廠商。

經濟現實與市場驅動力

開發 2nm 晶片的成本極其高昂,可能高達 1 億美元以上。然而,對於 AI 資料中心而言,能夠在單位功耗下處理更多數據是致勝關鍵。對於高階手機與 PC 市場而言,龐大的出貨量則可以攤提設計成本。

Rapidus 的 Beica 提到,客戶對於設計流程的參與度越來越高,部分客戶甚至希望自行設計,僅將製造與封裝交由代工廠整合。Rapidus 專注於單片晶圓處理(Single-wafer processing)而非批次處理,這使得他們能從每片晶圓獲得更多數據回饋至設計端,實現設計與製造的協同優化(DTCO),這對於縮短交期至關重要。

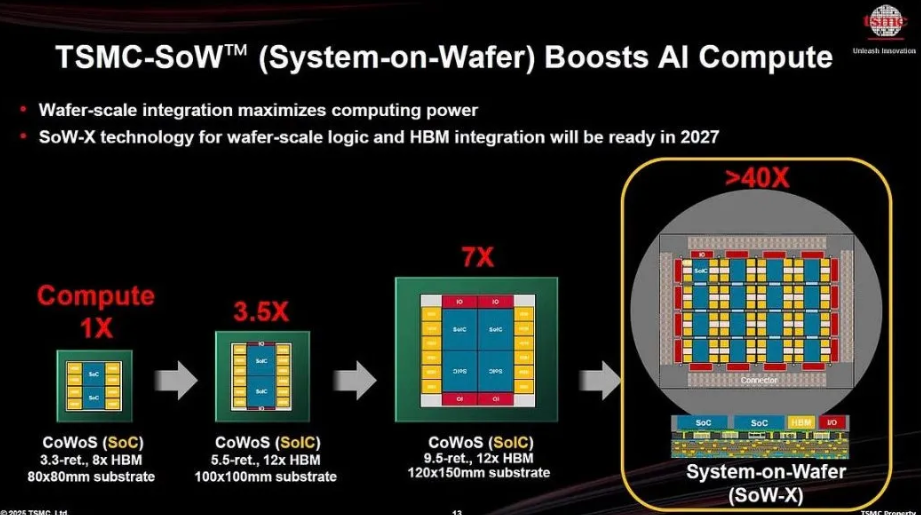

時間就是金錢。對於 AI 資料中心來說,透過大型矽中介層(Silicon Interposer)進行 2.5D 封裝雖然可行,但中介層越大,成本越高且訊號傳輸距離越長。雖然 3D 堆疊技術能縮短路徑,但開發時間更長。如何在各種製程節點的 CPU、GPU、NPU 之間取得平衡,考驗著工程師對物理效應的深刻理解。

總結來說,半導體產業邁向 2nm 的驅動力已不再單一。Lam Research 的 Fried 認為,歷史上某些節點擅長微縮功耗,有些擅長效能或面積,但在今天,最終的應用決定了優先順序。穿戴式裝置可能更在乎面積與成本,而電池供電設備則以功耗為中心。未來的晶片設計將是各種節點的混合體,以及在 PPA/C 之間進行全新權衡的藝術。這不僅是技術的升級,更是對半導體經濟學與系統架構的一次全面重構。

(首圖來源:Rapidus)