7 奈米、5 奈米的晶片金屬線徑微小、金屬間距極窄,修補過程中如何維持電性完整正確?

隨著摩爾定律,目前市面上可見到的晶片已從 10 奈米、7 奈米不斷微縮 5 奈米製程,宜特 FIB 電路修補實驗室,陸續收到 5 奈米(nm)製程,必須從晶背進行電路修改樣品。這是從 2018 年首度完成 7 奈米(nm)製程的樣品後,再次挑戰更先進製程的電路修補,並成功的完成挑戰,協助客戶進行晶片性能優化,加速產品上市。宜特科技將與您分享,如何藉由多年的成功經驗,完成 7 奈米、5 奈米等級以下的先進製程 IC 晶背電路修補技術。

速讀 FIB 電路修改技術(Focus Ion Beam)

FIB(Focus Ion Beam)聚焦離子束電子顯微鏡,是利用鎵(GA+)離子源透過電場牽引成離子束,高速碰撞樣品表面產生二次離、電子收集後成像;而離子轟擊過程中利用注入不同氣體,對晶片上各種材料進行選擇性地加速或減緩蝕刻,以及沉積導電和介電絕緣材料,達到修改電路的目的,搭配 CAD 導航系統輔助,準確的定位目標,提高電路修補精準度。

▲ 蝕刻機制(圖中)、沉積機制(圖右)。

一、IC 設計產業中不可或缺的戰略技術 – FIB 電路修補技術(Focus Ion Beam)

先進製程的開發成本越趨昂貴、晶圓產能短缺交期更長,即使電路模擬軟體(如 EDA 工具)的輔助設計不斷提升,仍無法確保晶片成品能百分之百達到設計目標,一旦發現電路瑕疵只能再次進行光罩改版;然而光罩價格不斐,且重新下光罩後,等待修改過後的晶片時間通常超過一個月,因此,多數 IC 設計業者,會選擇 IC 電路修補,只需幾個小時內即可完成修改,確保電路設計符合預期,並降低時間及金錢的成本耗損。

二、先進製程晶片金屬層間距極窄,難度大提升

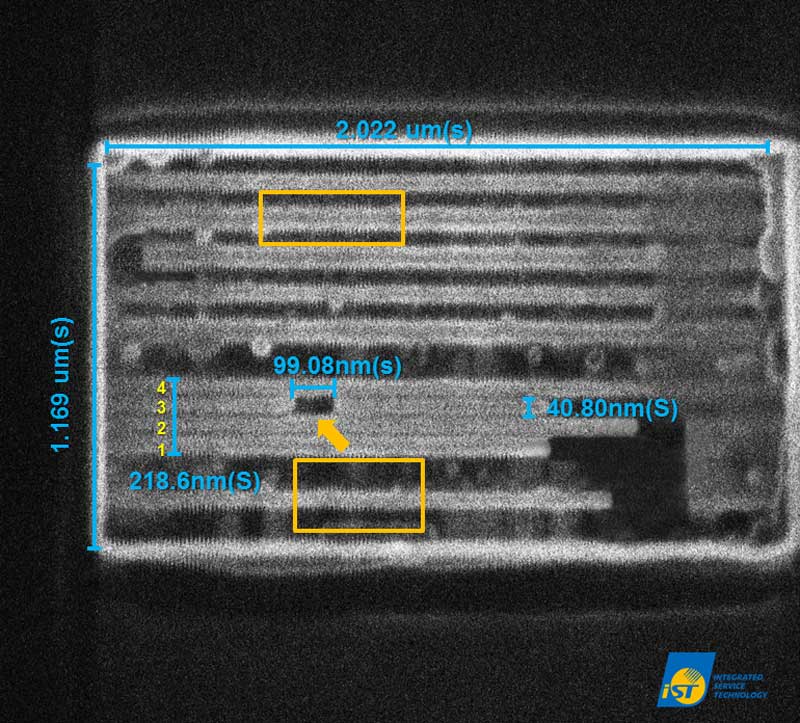

本案例的晶片電路修補,目的是要將 M1 的訊號斷路(圖一),目標點區域為最小金屬層設計尺寸(MMP),在 218nm 的距離內佈局 4 根訊號線。然而無論是 7nm 或 5nm 的晶片,金屬層的間距都相當窄(約小於 10nm),電路修補施工難度都相當高,令其他同業望 IC 興嘆、束手無策。

例如圖一,此為較不佳的先進製程電路修補案例,目標點蝕刻區域變形(藍色箭頭)、且周圍金屬層扭曲受損(黃線),以及底層暴露(白色箭頭),恐造成電路受損或短路等電性異常問題,大幅度降低電路修補成功率。

▲ 圖一:目標點蝕刻變形(藍色箭頭),金屬層扭曲且受損(黃線),多處底層暴露(白色箭頭)。

▲ 圖一:目標點蝕刻變形(藍色箭頭),金屬層扭曲且受損(黃線),多處底層暴露(白色箭頭)。

為了克服此先進製程電路修補難關,宜特利用極小 40*100nm 的空間(參見圖二,黃色箭頭處)精確地將目標點切除,更為困難的是兩側金屬層的間距極窄(約小於 10nm),在切除過程中,沒有因為緊鄰目標點而受到損傷破壞,維持電性完整正確,整體的困難度很高;若對比黃框標示位置,雖為同一金屬層,但兩側金屬間距大,施工難度相對較低。

▲ 圖二:影像清晰,極窄的間隙可清楚辨識,蝕刻移除空間(黃色箭頭)僅 40×100nm,且兩側金屬保留完整未受損;黃框位置與相鄰的金屬層間隙大,若進行切割難度降低許多。

▲ 圖二:影像清晰,極窄的間隙可清楚辨識,蝕刻移除空間(黃色箭頭)僅 40×100nm,且兩側金屬保留完整未受損;黃框位置與相鄰的金屬層間隙大,若進行切割難度降低許多。

三、如何克服先進製程晶片電路修補難關 – 從晶背著手

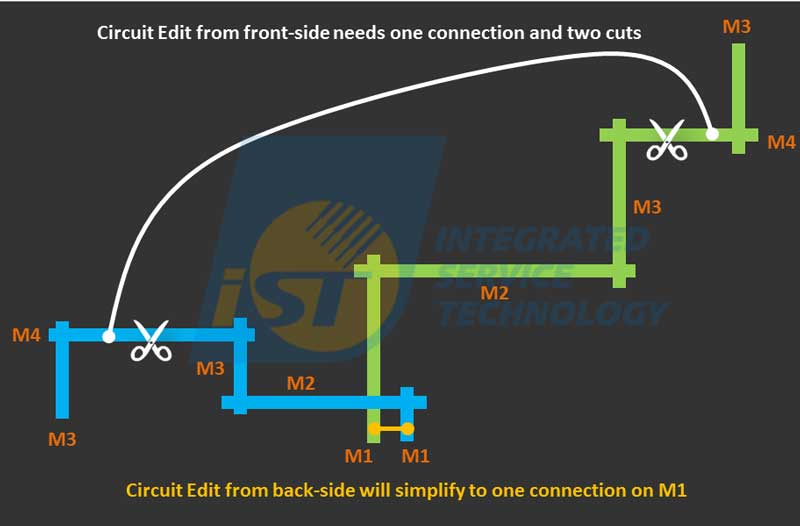

當先進製程發展至極小奈米,包裝型式多數為覆晶包裝技術(FCBGA、CIS-BSI 等)或稱「倒晶封裝」,晶片正面將有一層電路板基板(PCB Substrate),因此 FIB 電路修補就必須從晶背來執行,當從電路源頭來執行時,經常可簡化施工內容,以提高成功率(圖三)。

▲ 圖三:路徑追蹤示意圖,假設此先進製程為 9M+AP,從晶片正面(Front side)施工 M4,需要穿過 6 層金屬層(Metal:AP~M5)難度高;若改由晶背(Back side)方向,僅需穿過 Active Area(AA)層,並簡化內容在 M1 施工。

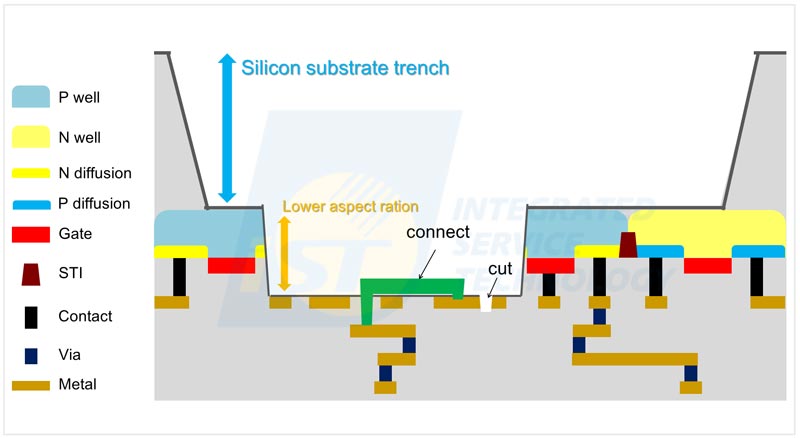

此外,從晶背施工還有幾項優勢,例如擁有低深寬比優勢,影像擷取較佳,精準度更高,施工工時縮短(參考圖四、五)。

再者,也可藉由縮短工時,減少離子束(GA+)對晶片長時間的電荷累積,而造成電路受損的疑慮,降低不可控因子導致的失效問題。

▲ 圖四:晶片剖面圖深度比較,Back side 有低深寬比的優勢。

▲ 圖四:晶片剖面圖深度比較,Back side 有低深寬比的優勢。

▲ 圖五:剖面示意圖,先削洗 silicon substrate trench 至 N well 暴露,縮小範圍針對目標點進行電路修改,且接近電路源頭,可簡化施工內容。

▲ 圖五:剖面示意圖,先削洗 silicon substrate trench 至 N well 暴露,縮小範圍針對目標點進行電路修改,且接近電路源頭,可簡化施工內容。

四、工欲善其事必先利其器 – 最先進的 FIB 電路修補工具

電路修補工具 – FIB 聚焦離子束設備能力,也隨著製程演進不斷的發展,無論在影像解析度、效能及準確度皆大幅提升。目前 FIB 工具搭配宜特電路修補技術不僅可完成 5nm 晶背電路修補外,Q1 引進的最新設備(設備能量請點此),其影像解析度更由 4.5nm 提升至 3.5nm,提高深層、微小線徑及複雜電路修補的成功率,並且其介電材料有更高的電阻率(1E15 uΩ-cm),絕緣效果更加強化,挑戰更先進製程。

宜特是台灣首家執行 FIB 電路修補的民營實驗室,翻轉 IC 設計業以往的驗證模式,大幅縮短 IC 設計公司從概念設計到量產上市時間並節省研發經費,成立至今,已替業界完成超過 369,130 顆晶片的電路修補,27 年的 FIB 電路修補經驗、搭配失效模式的大數據建立將如虎添翼,協助 IC 設計業者解決棘手的電路問題,本文與各位長久以來支持宜特的您,分享經驗,若您想要更進一步了解細節,歡迎洽詢 +886-3-5799909 分機 1068 邱小姐,Email: yuting_chiu@istgroup.com。

(圖片來源:宜特科技)