編按:資深前分析師 Richard 從財務面、技術面、競爭力分析等角度深度解析台積電,科技新報取得獨家授權,4 篇專文報導,帶你了解這間台灣舉足輕重的半導體巨擘。前三篇已就台積電的財務面、技術面、客戶面來做分析,最後一篇來說明它的競爭優勢。

Foundry 產業的關鍵競爭要素

1. 先進製程技術

半導體產業,只要摩爾定律(Moore’s Law)持續作用,必然讓更多功能、更多電晶體納入晶片中,而功能複雜的晶片,需要更先進微縮的製程技術,來降低 die size、降低成本,32 / 28nm 以前,每一世代 technology node 的 cost 都會降低,但到 20nm 和 14 / 16nm 的 cost per transistors 沒有降低多少,預期到了 10nm 和 7nm,cost per transistor 會再度明顯下降。除了成本之外,先進製程也可提高晶片的 performance / speed,和行動產品最重要的:降低耗電。

在邏輯製程(Logic process)半導體領域,通常會優先考慮使用最先進製程的產品包括:CPU、AP(Application processor)、GPU、FPGA / PLD,高整合度的複雜 SoC,其次是 Baseband、DSP、中整合度 SoC 等。誰能領先進入更先進的製程技術,就能吸引這些產品客戶來下單,客戶之間也是競爭對手,勢必和具有先進製程技術能力和未來研發潛力的 foundry 廠合作,才能維持客戶自身的競爭力。

先進製程的研發,除了研發投資金額越來越昂貴之外,更是基礎物理和半導體科學的競爭,有扎實深入的基礎研究,才能正確的預測幾年後、下一代的技術發展方向,然後投資下去,把這個技術開發出來商品化,將摩爾定律再往下推進,突破自己的製程競爭力,一旦對技術走向預測錯誤,不但會造成龐大的投資付諸流水,更會讓公司的技術發展落後對手,喪失競爭力。在先進製程研發領域,「博士」只是基礎訓練,製程實驗室戰場上面對的往往是「院士」級的對手。

2. 製造良率和效率

相較於先進製程技術,是由研發部門決定勝敗,生產效率和良率,則由製造部門負責,通常一個新的製程,不論是下一世代的先進製程(advanced technology node),或是水平發展的 specialty porcess,研發部門將新製程開發出來之後,將移交給製造部門負責,製造部門的工程能力非常重要,除了要和客戶 IC 設計研發人員密切配合,了解產品特性,也要對製程技術和機台特性透徹了解,才能快速提升客戶新產品的生產良率。

生產良率有 3 個重點,第一是良率爬升速度要快,第二是良率要高,例如,同樣新產品量產 3 個月時的良率高低,良率高代表創造更多價值,或者提高 foudnry 本身的毛利率,或者分享給客戶更低的價格,第三是良率的穩定性,有些 foundry 良率上來之後,忽上忽下,讓客戶很難生產規畫,良率時好時壞,隨時影響客戶的成本結構、業務能力和庫存政策,

再來,一家大型 foudnry 會有上百家客戶、上千項產品,同時間在晶圓廠內跑,產品組合、客戶組合、製程組合、每個製程又有很多複雜的生產流程,大批量、小批量的產品,通通混在廠內,生產管理要兼顧品質和效率,非常不容易,線上工程師面對不同產品的品質挑戰、交期挑戰、產出挑戰,尤其當各種各樣問題出現的時候,如何快速解決,都將在最後的效率上展現。

3. 客戶服務

foundry 的客戶是包括 Fabless、IDM 和 System house,每家客戶的產品變化很大,每家 foundry 業者的製程特性和 design rule 也都不相同,foundry 產業屬於客製化程度很高、服務性質很高的產業 。客戶對 foundry 廠的需求包括:幫助客戶熟悉 foundry 製程的 design rule、幫助客戶設計出很容易製造併提高良率的 IC、幫助客戶依據製程發展藍圖規劃自己的產品藍圖、基本 IP 支援、良好的 EDA / tools 環境、良率快速拉升、良率穩定、交期準確、成本 / 價格有競爭力、生產問題解決、生產資訊的分享、產能投資承諾、技術研發投資承諾等。

台積電競爭力分析

1. 台積電的先進製程技術能力

邏輯製程的先進製程技術,英特爾還是第一名,但台積電和 Samsung LSI 急起直追,3 家公司都預計在 End-2016 量產 10nm,但英特爾可能率先進入下一代新的電晶體架構,如同英特爾在 22nm 率先進入 3D transistors,台積電和 Samsung LSI 到 14 / 16nm 才進入 3D transistors,而英特爾雖然 10nm 量產時間沒有繼續領先,但可能在 10nm 採用新一代的 Gate-all-around 架構,台積電和 Samsung LSI 則繼續用 3D FinFET 架構。

台積電這兩年製程技術,已經超越 IBM,Samsung LSI 本來屬於 IBM 技術聯盟,28nm 時和 IBM 一樣用 Gate First 技術,不像英特爾和台積電用 Gate Last 技術,後來承認錯誤,IBM 聯盟廠包括 Samsung LSI 到 20 / 22nm 才改回來用 Gate Last,加上 20nm 市場幾乎被台積電通吃,累積不少經驗,Samsung LSI 則沒有 20nm 大量產經驗,要從 28nm Gate First,直接跳到 14nm Gate Last,有其困難度,這應該也是台積電之所以輕敵的原因。

不料,Samsung LSI 的 14nm 做得出奇的好,量產時間領先台積電 1~2 季,台積電從早年的英特爾第一、IBM 第二、台積電第三名,一度追成英特爾第一、台積電第二、IBM 變成第三名,到 2015 年又變成英特爾第一、Samsung LSI 第二、台積電再度淪為第三名。從此,Samsung LSI 正式變成台積電在先進製程研發上面的強勁對手。未來勝負很難預料。

從基本研發實力分析,台積電人才濟濟,研發部門博士碩士只是基本履歷,重量級的「院士」 、半導體學術界的重量級論文、關鍵專利創作者,都具有相當份量,是台積電先進製程研發的重要優勢。十幾年來台積電在技術發展方向上,幾乎都走在正確的道路,一一過關斬將,終於拉近和英特爾的技術落差,真正進入世界一流先進製程技術公司的決賽圈。

每一次選擇正確的技術方向,都是重大戰役,台積電目前的紀錄無懈可擊,例如,0.13um 銅製程 low K 材料,台積電正確選擇以 FSG 材料為基礎的,Applied Material 的 Black Diamond(IBM / UMC / Infineon 選擇 Dow Chemica 的 SILK),High speed / CPU 製程主力選擇放在 Bulk CMOS(IBM / AMD / Chartered 選擇 SOI),45nm 開始將主力放在 40nm half-node,32 / 28nm 世代和 22 / 20nm 更直接只量產 half-node 28nm 和 20nm,45 / 40nm 選擇 Gate Last(IBM 聯盟 Samsung / Globalfoundries 等全部選擇 Gate First)。

當全球半導體界受阻於 65 / 55nm 以下 193nm 波長微影極限,重金研發 157nm 乾式光微影(optical lithography)遲遲無法突破時,台積電林本堅院士提出繼續用 193nm 但改用浸潤式微影(Immersion Lithography),完全主導業界技術走向,將製程技術順利推向 45nm 以下,透過多重曝光,193nm 波長浸潤式微影 scanner 機台甚至確定可以做到 10nm 還沒問題。至於今年台積電、Samsung LSI 開始量產的 FinFET 3D 電晶體,其發明人胡正明院士也曾於 2001~2004 年任職台積電。

接下來下一製程技術的大戰,就是何時開始用 EUV 微影,台積電目前規劃 10nm 製程不用 EUV,7nm 開始試用,5nm 才全面使用,EUV 從 32 / 22nm 就開始研發,台積電似乎有信心將 193nm 波長浸潤式微影,繼續推進到 7nm,屆時,台積電的 193nm 波長浸潤式微影 7nm,將和英特爾的 EUV 微影 7nm 對決。

2. 台積電的製造能力

先進製程通常只有 1~2 家少數對手,彼此爭取為數很少和但訂單量大的大客戶,主要競爭在新製程量產時程和良率,但成熟製程的 foundry 對手多,主要競爭在製造能力,台積電的製造能力展現在以下幾點:

- 產品投產後良率拉升快:客戶可 time to market。

- 平均良率高:雖然台積電 wafer 報價比對手高,但良率高 good die 產出也多,實際價差沒有那麼大。

- 良率穩定:客戶銷售和庫存管理負擔輕。

- 所有製程都是自行研發,製程參數資料庫完整,RD 知其然也知其所以然,不像UMC、Globalfoundries 的部份製程技術是和別人合作或授權,出問題很難調整,大案子可以由 RD 人員特別客製化,但推廣到幾十、幾百個大小案子時,就不能事事靠 RD,必須製造部門自己解決,授權來的製程技術,很多細節要慢慢摸索消化吸收。

- 製程 portifolio 完整,28nm 橫向發展各種應用或 cost down 新版,其他 specialty 製程也很廣泛。

- 生產流程效率化、自動化,在一家有幾百個產品同時生產的 foundry,尤顯重要。

- 因為生產管理和良率上軌道,交貨(delivery)能力強。

- Fab 12(新竹)、Fab 14(台南)、Fab 15(台中)三大超大晶圓廠(Giga Fabs)有降低生產成本、縮短 cycle time、提高生產彈性等好處,資深人力的調度、支援也是無形的好處。

- 台灣半導體廠共有的另一項優勢,做二休二,這種制度讓工廠一天只要輪兩班,不用輪三班,狀況、問題只有兩批人交接,不是三批人交接,會比較順利,責任也比較容易釐清,做二休二對生產效率和品質控管的好處,很少人提到,但個人認為這是台灣獨特的地方。

- 生產線工程師素質高:台積電生產線上有很多一流大學甚至碩士學歷的工程師,基層工程師素質高於國外半導體廠,就國家資源分配的角度,有點殺雞用牛刀,但對台積電則無疑是加分的。

3. 台積電的製程設備共用性

台積電的 20nm 和 16nm 技術經驗沿用性很高,設備也有 95% 可以共用。10nm 是下一個階段,投資額可能比較大,但跨過 10nm 之後,10nm 和 7nm 技術經驗沿用性也很高,設備也有 90% 可以共用。這應該不是產業普遍的現象,牽涉到新製程開始研發的時候,就要考量到設備共用性,還有對設備的了解和知識,才有修改設備沿用到下一世代製程的能力。不是每個人都可以做到的。推估,這是台積電長年和設備廠商共同研發先進製程設備所累積的經驗,和積極 cost down 創造利潤和高 ROE 的企業文化使然。至於英特爾和 Samsung LSI 有沒有這種考量,不得而知,但他們是 IDM 出身,理論上比較重視技術領先第一,至於要不要在技術領先的同時,考量到設備共用的成本節省,恐怕未必。

台積電 2016 年仍可成長 5~10%

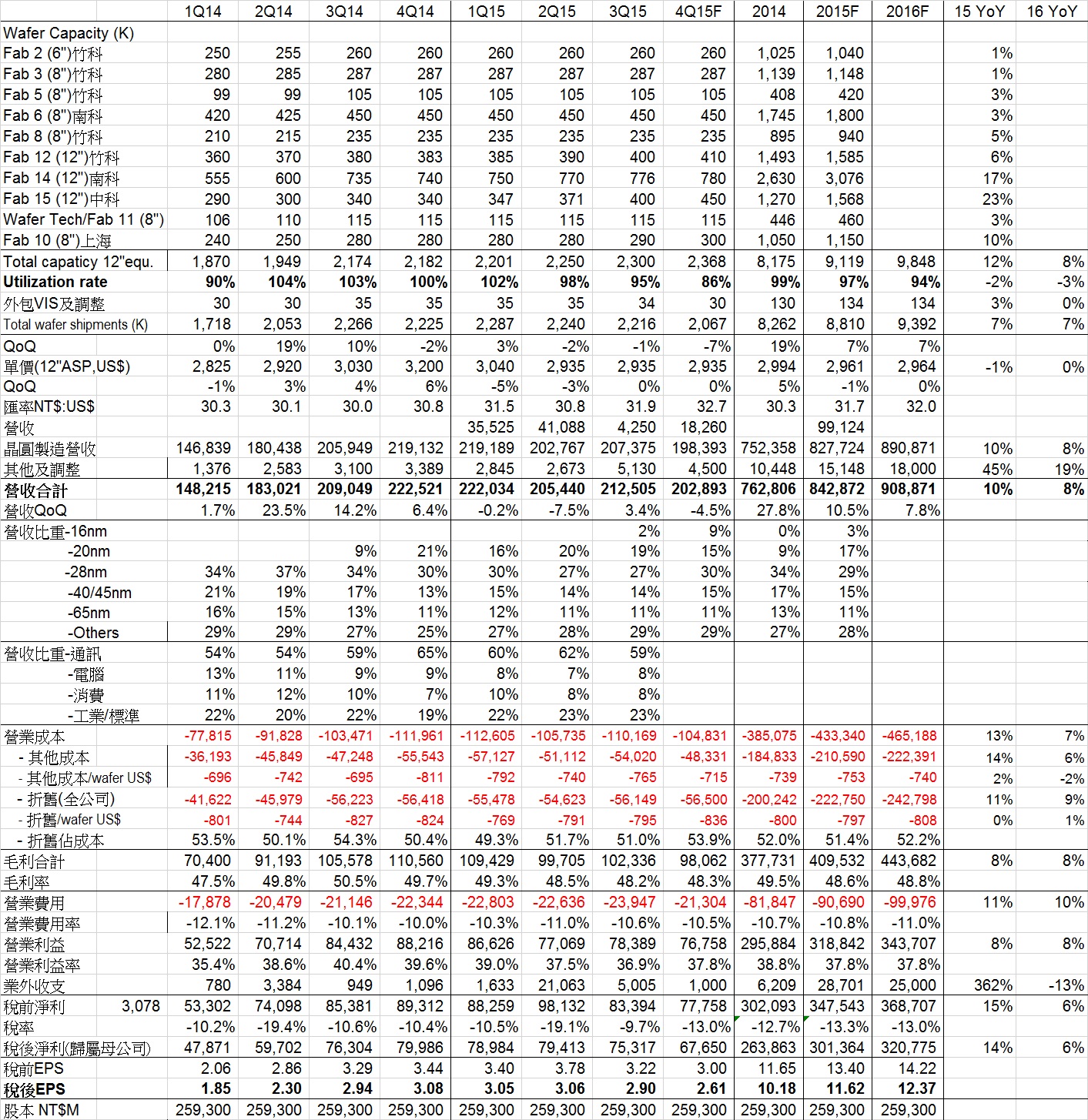

假設 2016 年台積電產能成長 8%、平均產能利用率 94%、Blended ASP 持平、匯率 32,則營收估計 9,089E,成長 8%。假設折舊增加 9%、其他成本 per wafer US$740,毛利率約 48~49%、OP% 37~38%、稅後淨利 3,208E,成長 6%。

(全文完;本文由 Richard’s Research Blog 授權轉載;首圖來源:達志影像)