人工智慧(AI)浪潮席捲全球,帶動高階 AI 伺服器需求急劇增長,推升 GPU 運算能力、SoC 與龐大 HBM 記憶體系統的整合需求。然而,隨著 AI GPU 晶片尺寸不斷擴大,晶片互聯與 I/O 數量呈指數級增長,使得現有 12 吋晶圓級封裝產能面臨前所未有的壓力,台積電獨霸市場的 CoWoS 封裝技術亦逐漸遭遇成長天花板。為了突破產能與物理極限的瓶頸,台積電正積極推進次世代面板級封裝技術 CoPoS( Chip-on-Panel-on-Substrate),這項被譽為 「化圓為方」 的技術變革,預計將於 2026 年啟動測試線,並在 2028 年邁入量產,重新定義未來十年的 AI 晶片封裝遊戲規則。

CoWoS 逼近物理極限,產能擴充遭遇瓶頸

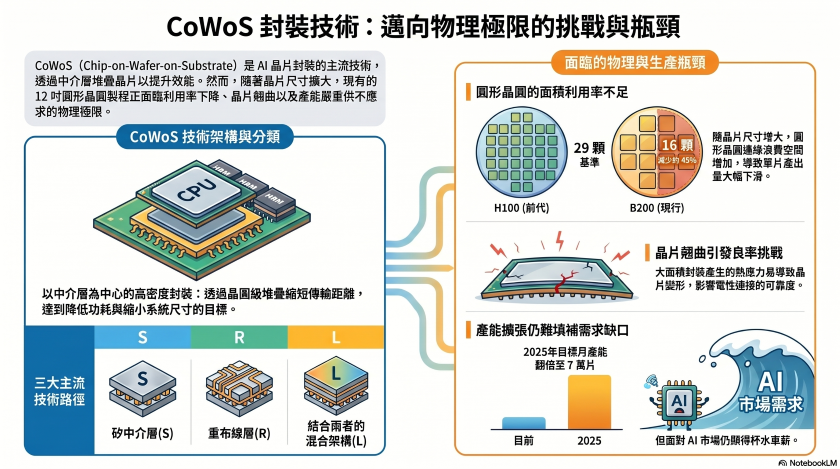

現有的 CoWoS(Chip-on-Wafer-on-Substrate) 技術是一種以中介層 (Interposer) 為中心的高密度封裝架構,透過在晶圓階段將多顆晶片進行堆疊與連結,以縮短訊號傳輸距離並同時降低功耗與系統尺寸。依照中介層材質不同,可分為採用矽中介層的 CoWoS-S、採用重布線層 (RDL) 的 CoWoS-R,以及混合矽與 RDL 設計的平衡架構 CoWoS-L。

儘管 CoWoS 在 AI 晶片封裝領域稱霸,但以 「12 吋圓形晶圓」 為基礎的製程正面臨嚴峻挑戰。首先是面積利用率嚴重不足,在處理大尺寸的方形 AI 晶片時,圓形晶圓的邊緣會產生大量浪費空間。數據顯示,以輝達 (NVIDIA)B200 晶片為例,在一片 12 吋晶圓上僅能放置 16 顆,相較於前代 H100 晶片可放置的 29 顆大幅下降,這反映出晶片尺寸增長與現有產能的根本矛盾。

其次是晶片翹曲現象所帶來的良率挑戰。隨著 AI 晶片面積不斷擴大,封裝過程中的熱應力極易導致晶片彎曲變形,進而影響電性連接的可靠度與測試良率。此外,即便台積電積極擴產,2024 年底 CoWoS 月產能達 3.5 萬片,2025 年目標為 7 萬片,面對龐大的市場需求仍顯得杯水車薪。法人報告亦曾指出,由於 CoWoS 封裝技術逼近物理極限,市場對新一代先進封裝技術的關注度正急速升溫。

化圓為方 CoPoS 技術架構與面板級封裝優勢

為了解決傳統晶圓產能不夠且成本持續提升的問題,業界催生了 「CoWoS 面板化」 的概念,而台積電的解答正是 CoPoS 技術。CoPoS 本質上是 CoWoS 的面板化演進版本,核心概念是採用方形的 「面板 RDL 層」 取代傳統圓形矽中介層,晶片可直接排列於矩形的基板上,透過 「化圓為方」 大幅提升面積利用率與生產效率。

面板級封裝能提供更高的產能與更低的生產成本,其中以 510×515mm 的方形面板為例,其可放置空間是 12 吋晶圓的 4.5 倍。若採用 600×600mm 面板則為 6 倍,700×700mm 更可達 8 倍之多。目前業界逐步推動的主流尺寸方向,包括3 10×310mm、515×510mm 及750×620mm 等多種規格。

在技術架構上,CoPoS 結合了 CoWoS-L 與 CoWoS-R 的優勢,採取模組化封裝架構,先將晶片依功能整合為模組並完成測試,再配置於大型基板上,有助於突破封裝尺寸與效能瓶頸,提升整體系統效率。特別值得注意的是,CoPoS 中介層材料將改為玻璃或藍寶石等高穩定性介質的方形載具,搭配多層 RDL 技術。玻璃基板具備低熱膨脹係數、高機械強度、耐高溫與高佈線密度等特性,能有效改善大尺寸晶片的翹曲變形問題並提升散熱能力,同時透過玻璃基板的 TGV(Through Glass Vias) 製程,形成連接上下電路的導電層。

此外,CoPoS 與同屬面板級封裝的 FOPLP(扇出型面板級封裝) 有著明確的高低階市場區隔。CoPoS 專攻需要中介層設計的 AI 高階晶片市場,能提供更高訊號完整性與穩定功率傳輸,適合多個高性能、高功耗晶片整合。而 FOPLP 則不需中介層結構,鎖定 PMIC(電源管理晶片)、RFIC(射頻晶片) 等低成本與汽車電子應用領域。

2026 年測試線啟動,2028 年嘉義廠領軍量產

晶圓代工龍頭台積電對於 CoPoS 的推進時程與全球佈局已然明朗,預計於 2026 年在專精先進封裝的台積電子公司采鈺設立首條 CoPoS 實驗線,隨後於 2027 年進入關鍵送樣階段,針對合作夥伴需求優化製程參數。量產階段預定於 2028 年底至 2029 年上半年啟動,主要生產基地將落腳於台積電最新且規模最大的先進封裝據點-嘉義 AP7 廠,且首家客戶已確定為輝達。

嘉義 AP7 廠規劃有 8 座廠房,採取分階段建設的多元化策略以避免技術風險集中,其中 P1 專門生產蘋果 WMCM,P2、P3 鎖定 SoIC(3D 封裝) 技術,而 CoPoS 技術則暫定部署於 P4 或 P5 廠房。台積電的國際佈局亦同步展開,預計 2028 年動工的美國亞利桑那州 2 座先進封裝廠,將各自專精 SoIC 與 CoPoS 技術。另外加上近期整併竹科舊有廠房評估改建為先進封裝設施,整體先進封裝產能規劃目標將從 2024年底的 3.5 萬片,至 2026 年大幅提升至 11 萬片。

設備與供應鏈受惠,引爆全球千億商機

CoPoS 量產計畫確立,不僅推動技術升級,更帶動全球設備供應鏈的競標熱潮。產業估算,單條 CoPoS 產線設備投資金額約需新台幣 100 至 150 億元,若台積電按規劃建設5 至 8 條產線,加上美國廠區的同步建設,全球 CoPoS 設備市場總規模預估將超過 2,000 億元新台幣,為相關廠商創造龐大商機。

在國際設備大廠方面,包括 KLA、TEL、Screen、應用材料、Disco、Canon 等 13 家廠商已率先入列,涵蓋檢測、蝕刻、塗佈、切割等關鍵製程。台灣本土供應鏈同樣有望共享先進封裝紅利,受惠的製程設備、材料與周邊檢測廠包括印能、辛耘、弘塑、均華、志聖、大量、群翊、牧德、晶彩科、倍利科、鈦昇及晶呈科技等眾多業者。

其中,關鍵的 RDL(重佈線層) 技術門檻最高,需要包含濕式清洗、顯影、蝕刻、剝除、電鍍等全套設備解決方案。在封測廠端,法人也點名日月光投控、力成 、京元電子、群創 及矽格等將成為下一世代封裝方案的潛在受惠者。

面對 AI 晶片朝大尺寸、高整合度發展,台積電這項 「化圓為方」 的戰略,不僅僅是簡單的幾何變革,更是重新定義半導體封裝遊戲規則的核心技術。預期在 2028 年量產啟動後,能在此次方形革命中站穩腳步的企業,將掌握下一個十年 AI 晶片封裝的話語權,這同時也是台灣鞏固全球半導體供應鏈戰略地位的重要契機。

(首圖來源:AI)