台積電開放創新平台 3DFabric 聯盟迎接新生力軍,imec 旗下 IC-Link 正式加入 |

| 作者 Atkinson|發布日期 2026 年 05 月 13 日 11:15 | 分類 IC 設計 , 半導體 , 晶圓 |

Tag Archives: imec

imec 宣布輝達黃仁勳獲頒 2026 年度終身創新獎 |

| 作者 Atkinson|發布日期 2026 年 03 月 26 日 7:00 | 分類 AI 人工智慧 , GPU , IC 設計 |

比利時微電子研究中心(imec)宣布,GPU大廠輝達 (NVIDIA) 創辦人暨執行長黃仁勳獲頒 2026 年 imec 年度終身創新獎(Lifetime of Innovation Award)。imec 藉由這個獎項表揚黃仁勳為實現高速運算技術和推動各大產業的關鍵 AI 應用所發揮的重要作用──圖形處理器(GPU)的發明是這些成果的發展動能。此次頒獎典禮包含與黃仁勳進行視訊採訪,將於 5 月 19 日在比利時安特衛普(Antwerp)imec 全球技術論壇(ITF World) 上舉行。

聯電提升成熟製程價值,新加坡新廠發展矽光子 2027 年量產 |

| 作者 Atkinson|發布日期 2026 年 01 月 20 日 10:45 | 分類 AI 人工智慧 , 半導體 , 封裝測試 |

開創生醫應用新局,imec 靠 ASML EUV 設備成功實現晶圓級奈米孔 |

| 作者 林 妤柔|發布日期 2025 年 12 月 22 日 13:33 | 分類 半導體 , 材料、設備 |

比利時微電子研究中心(imec)已成功展示利用 ASML 最先進的極紫外光(EUV)微影設備,實現晶圓級規模的奈米孔製作技術。ASML 傳播主管形容,由於奈米孔在分子感測領域展現的巨大潛力,這是 ASML 設備「出乎意料卻非常令人驚豔的生醫應用」。 繼續閱讀..

Imec 展示首次利用 EUV 微影實現的固態奈米孔的晶圓級製造 |

| 作者 PR Newswire|發布日期 2025 年 12 月 14 日 14:00 | 分類 半導體 , 市場動態 , 晶圓 |

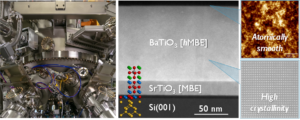

Imec 成功實現了首次在 300 毫米晶圓上利用 EUV 微影技術進行固態奈米孔的晶圓級製造。這項創新將奈米孔技術從實驗室規模的概念,轉化為用於生物感測、基因組學和蛋白質組學的可擴展平台。

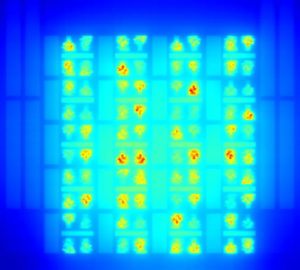

Imec 系統─技術協同最佳化方案,緩解 3D HBM-on-GPU 架構的散熱瓶頸 |

| 作者 PR Newswire|發布日期 2025 年 12 月 13 日 14:00 | 分類 半導體 , 市場動態 , 晶片 |

全面系統─技術協同最佳化(STCO),是降低 AI 工作負載下 GPU 和 HBM 峰值溫度,同時提升未來 GPU 架構的效能密度的關鍵。 繼續閱讀..