積極留才!聯電宣布即日起施行 5 萬張庫藏股計畫 |

| 作者 Atkinson|發布日期 2026 年 04 月 29 日 21:00 | 分類 公司治理 , 半導體 , 晶圓 |

Category Archives: 處理器

英特爾財報亮眼帶動上週美股半導體族群攻堅,有助本週台股開盤期待 |

| 作者 Atkinson|發布日期 2026 年 04 月 27 日 7:30 | 分類 AI 人工智慧 , GPU , IC 設計 |

隨著市場對人工智慧(AI)需求的樂觀情緒再次升溫,輝達(Nvidia)股價在上週五股價飆升 4.8%,收盤價達到 209.18 美元,並帶動美股道瓊工業平均指數。該公司盤中股價更一度觸及 210.95 美元,創下 2025 年 11 月以來的最強勁水準,正朝著歷史收盤新高邁進。市場分析,此次半導體類股的全面反彈,主要歸功於英特爾(Intel)強勁的財報表現,也為27日的台股開盤注入新的期待。

大摩看好非 GPU 伺服器資本支出效益大,給予股王信驊 15,555 元天價目標價 |

| 作者 Atkinson|發布日期 2026 年 04 月 21 日 9:50 | 分類 AI 人工智慧 , GPU , IC 設計 |

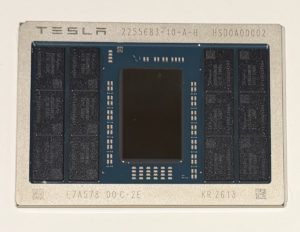

馬斯克秀 AI5 處理器樣品稱性能較前代飆升 40 倍,感謝「TSC」成意外插曲 |

| 作者 TechNews 編輯台|發布日期 2026 年 04 月 16 日 8:40 | 分類 汽車科技 , 自駕車 , 處理器 |

因為這點,三星 2025 年不得不讓 Exynos 2600 處理器上陣 |

| 作者 Atkinson|發布日期 2026 年 04 月 14 日 15:40 | 分類 Samsung , 半導體 , 處理器 |

根據韓國媒體報導,科技大廠三星(Samsung)正加速邁向晶片自主化,其首款 2 奈米 GAA 系統單晶片(SoC)Exynos 2600 已正式搭載於部分 Galaxy S26 與 Galaxy S26+ 機型中。不過,市場消息指出,這項重大戰略決策的背後,源於三星在 2025 年為 Galaxy S25 系列向高通(Qualcomm)採購 Snapdragon 8 Elite 晶片,導致了高達 30 億美元的驚人虧損。為避免持續受制於外部供應商,三星已決心重振其晶片部門,確保不再單一依賴其他公司。

SK 電信聯手 Arm 與 Rebellions 打造更高效 AI 伺服器,搶攻 AI 基建市場 |

| 作者 TechNews 編輯台|發布日期 2026 年 04 月 13 日 10:10 | 分類 AI 人工智慧 , GPU , 伺服器 |

SK 電信 9 日宣布,與英國 Arm 及韓國 Rebellions 簽署合作備忘錄,共同開發結合中央處理器(CPU)和神經處理單元(NPU)的人工智慧伺服器解決方案,提升 SK 電信人工智慧資料中心競爭力,並加速自主 AI 生態系統發展。 繼續閱讀..

淺談 Snapdragon X2 Elite:見樹不見林? |

| 作者 朱熹|發布日期 2026 年 04 月 13 日 7:50 | 分類 半導體 , 處理器 |

Snapdragon X2 Elite 評測近日出爐,在處理器效能和電池續航的表現上,這顆高通第二度衝擊 WoA 市場的晶片都可圈可點,且其以往最大的詬病──軟體相容性和遊戲性能也有所改善,所以大部分的媒體均給予好評。但筆者卻逆風地認為這又是一個典型的見樹不見林的集體失焦,究竟是為什麼?